Automatizace elektronického designu - Electronic design automation

Electronic Design Automation ( EDA ), také označovaný jako elektronický počítačem podporovaný design ( ECAD ), je kategorie softwarových nástrojů pro navrhování elektronických systémů, jako jsou integrované obvody a desky s plošnými spoji . Nástroje spolupracují při návrhu, který návrháři čipů používají k návrhu a analýze celých polovodičových čipů. Protože moderní polovodičový čip může mít miliardy součástek, jsou nástroje EDA pro jejich návrh zásadní; tento článek popisuje zejména EDA konkrétně s ohledem na integrované obvody (IC).

Dějiny

Brzké dny

Před vývojem EDA byly integrované obvody navrženy ručně a ručně rozloženy. Některé pokročilé obchody používaly ke generování pásek pro fotoplotter Gerber zodpovědný za generování monochromatického expozičního obrazu geometrický software , ale i ty kopírované digitální záznamy mechanicky kreslených součástí. Proces byl v zásadě grafický, přičemž překlad z elektroniky do grafiky byl prováděn ručně; nejznámější společností z této éry byla Calma , jejíž formát GDSII se používá dodnes. V polovině 70. let začali vývojáři kromě navrhování automatizovat i návrh obvodů a byly vyvinuty první nástroje pro umísťování a směrování ; jak k tomu došlo, sborník konference Design Automation Conference katalogizoval velkou většinu vývoje té doby.

Další éra začala po vydání „Úvod do systémů VLSI “ od Carver Mead a Lynn Conway v roce 1980; tento průkopnický text obhajoval návrh čipů s programovacími jazyky, které byly kompilovány do křemíku. Okamžitým výsledkem bylo značné zvýšení složitosti čipů, které bylo možné navrhnout, se zlepšeným přístupem k nástrojům pro ověřování návrhu, které používaly logickou simulaci . Čipy se často snáze rozkládaly a pravděpodobněji fungovaly správně, protože jejich konstrukce bylo možné před stavbou důkladněji simulovat. Ačkoli se jazyky a nástroje vyvíjely, zůstává tento obecný přístup určování požadovaného chování v textovém programovacím jazyce a ponechání nástrojů odvozovat podrobný fyzický design základem digitálního návrhu IC dnes.

Nejstarší nástroje EDA byly vyrobeny akademicky. Jedním z nejznámějších byl „Berkeley VLSI Tools Tarball“, sada nástrojů UNIX používaných k návrhu raných systémů VLSI. Stále široce používané jsou heuristický logický minimalizátor Espresso , zodpovědný za snížení složitosti obvodů, a Magic , počítačem podporovaná návrhová platforma. Dalším zásadním vývojem bylo vytvoření MOSIS , konsorcia univerzit a výrobců, kteří vyvinuli levný způsob, jak školit návrháře studentských čipů výrobou skutečných integrovaných obvodů. Základním konceptem bylo použití spolehlivých, levných, relativně nízko technologických IC procesů a zabalení velkého počtu projektů na oplatku , přičemž několik kopií čipů z každého projektu zůstalo zachováno. Spolupracující výrobci buď zpracované oplatky darovali, nebo je prodali za cenu. protože viděli program užitečný pro jejich vlastní dlouhodobý růst.

Zrození komerční EDA

1981 znamenal začátek EDA jako průmyslového odvětví. Po mnoho let se větší elektronické společnosti, jako Hewlett Packard , Tektronix a Intel , zabývaly EDA interně, přičemž manažeři a vývojáři z těchto společností začali vycházet, aby se soustředili na EDA jako podnikání. Daisy Systems , Mentor Graphics a Valid Logic Systems byly založeny v této době a souhrnně označovány jako DMV. V roce 1981 americké ministerstvo obrany navíc začalo financovat VHDL jako jazyk hardwarového popisu. Během několika let existovalo mnoho společností specializujících se na EDA, každá s trochu jiným důrazem.

První veletrh pro EDA se konal na konferenci Design Automation Conference v roce 1984 a v roce 1986 společnost Gateway Design Automation jako jazyk popisu hardwaru poprvé představila Verilog , další populární designový jazyk na vysoké úrovni . Simulátory tyto úvody rychle následovaly, což umožňovalo přímou simulaci návrhů čipů a spustitelných specifikací. Během několika let byly vyvinuty back-endy k provádění logické syntézy .

Aktuální stav

Aktuální digitální toky jsou extrémně modulární, přičemž frontendy produkují standardizované popisy designu, které se komplikují do vyvolání jednotek podobných buňkám bez ohledu na jejich individuální technologii. Buňky implementují logiku nebo jiné elektronické funkce pomocí konkrétní technologie integrovaných obvodů. Výrobci obecně poskytují knihovny komponent pro své výrobní procesy se simulačními modely, které odpovídají standardním simulačním nástrojům.

Většina analogových obvodů je stále navrhována ručně, což vyžaduje speciální znalosti, které jsou jedinečné pro analogový design (například odpovídající koncepty). Analogové nástroje EDA jsou tedy mnohem méně modulární, protože je zapotřebí mnohem více funkcí, interagují silněji a komponenty jsou obecně méně ideální.

EDA pro elektroniku rychle roste na důležitosti s kontinuálním škálováním polovodičové technologie. Někteří uživatelé jsou slévárenští operátoři, kteří provozují zařízení na výrobu polovodičů (dále jen „fabie“), a další jednotlivci odpovědní za využívání společností zabývajících se návrhem technologie, které používají software EDA k vyhodnocení příchozího návrhu na připravenost výroby. Nástroje EDA se také používají k programování funkcí návrhu do FPGA nebo do programovatelných hradlových polí, přizpůsobitelných návrhů integrovaných obvodů.

Software se zaměřuje

Design

Návrhový tok zůstává primárně charakterizován prostřednictvím několika primárních komponent; tyto zahrnují:

- Syntéza na vysoké úrovni (dále známá jako behaviorální syntéza nebo algoritmická syntéza)-Popis návrhu na vysoké úrovni (např. V C/C ++) je převeden na RTL nebo úroveň přenosu registru, která odpovídá za reprezentaci obvodů využitím interakcí mezi registry.

- Logická syntéza - překlad popisu návrhu RTL (např. Napsaného ve Verilogu nebo VHDL) do diskrétního netlistu nebo reprezentace logických bran.

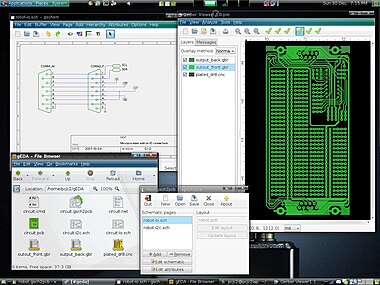

- Schematické zachycení -Pro standardní digitální, analogový, RF Ct Capture CIS v Orcad od Cadence a ISIS v Proteus.

- Layout -obvykle schematicky řízené rozložení , jako Layout v Orcad od Cadence, ARES v Proteus

Simulace

- Simulace tranzistoru-simulace tranzistoru na nízké úrovni chování schématu/rozvržení, přesná na úrovni zařízení.

- Logická simulace -digitální simulace digitálního chování RTL nebo gate-netlistu ( boolean 0/1), přesná na booleovské úrovni.

- Behaviorální simulace-simulace architektonické operace návrhu na vysoké úrovni, přesná na úrovni cyklu nebo na úrovni rozhraní.

- Emulace hardwaru - Použití hardwaru pro speciální účely k emulaci logiky navrhovaného návrhu. Někdy může být zapojen do systému místo dosud nevybudovaného čipu; tomu se říká emulace v obvodu .

- Technologie CAD simuluje a analyzuje základní technologickou technologii. Elektrické vlastnosti zařízení jsou odvozeny přímo z fyziky zařízení.

- Řešiče elektromagnetického pole , nebo jen pole , řeší Maxwellovy rovnice přímo pro případy zájmu o návrh IC a PCB. Je známo, že jsou pomalejší, ale přesnější než extrakce rozložení výše.

Analýza a ověření

- Funkční ověření

- Ověření křížení domény hodin (kontrola CDC): podobné lintingu , ale tyto kontroly/nástroje se specializují na detekci a hlášení potenciálních problémů, jako je ztráta dat , meta-stabilita díky použití více hodinových domén v návrhu.

- Formální ověření , také kontrola modelu : pokusy dokázat matematickými metodami, že systém má určité požadované vlastnosti a že nemůže dojít k určitým nežádoucím účinkům (například zablokování ).

- Kontrola ekvivalence : algoritmické srovnání mezi popisem RTL čipu a syntetizovaným seznamem bran , aby byla zajištěna funkční ekvivalence na logické úrovni.

- Statická analýza časování : analýza časování obvodu způsobem nezávislým na vstupu, a proto nalezení nejhoršího případu ze všech možných vstupů.

- Fyzické ověření , PV: kontrola, zda je návrh fyzicky vyrobitelný a zda výsledné čipy nebudou mít žádné fyzické vady zabraňující funkcím a budou splňovat původní specifikace.

Příprava výroby

-

Příprava dat masky nebo MDP - Generování skutečné litografické fotomasky , používané k fyzické výrobě čipu.

- Dokončování čipů, které zahrnuje vlastní označení a struktury pro zlepšení vyrobitelnosti rozvržení. Příklady posledně jmenovaných jsou těsnicí kroužek a výplňové struktury.

- Vytvoření rozložení záměrné osnovy pomocí testovacích vzorů a značek zarovnání.

- Příprava rozvržení na masku, která vylepšuje data rozvržení grafickými operacemi, jako jsou techniky vylepšení rozlišení nebo RET-metody pro zvýšení kvality finální fotomasky . To také zahrnuje optickou korekci přiblížení nebo OPC-přední kompenzace difrakčních a interferenčních efektů, ke kterým dochází později při výrobě čipu pomocí této masky.

- Generování masky - Generování obrazu ploché masky z hierarchického designu.

- Automatické generování testovacích vzorů nebo ATPG-Generování vzorových dat systematicky pro cvičení co největšího počtu logických bran a dalších komponent.

- Vestavěný autotest nebo BIST-instalace samostatných testovacích řadičů k automatickému testování logické nebo paměťové struktury v návrhu

Funkční bezpečnost

- Analýza funkční bezpečnosti , systematický výpočet rychlostí selhání (FIT) a metriky diagnostického pokrytí návrhů za účelem splnění požadavků na shodu pro požadované úrovně integrity bezpečnosti.

- Syntéza funkční bezpečnosti , přidejte vylepšení spolehlivosti strukturovaných prvků (moduly, RAM, ROM, registrační soubory, FIFO) pro zlepšení detekce chyb / odolnosti vůči chybám. Patří sem (nejen) přidání detekce chyb a / nebo opravných kódů (Hamming), nadbytečná logika pro detekci chyb a odolnost proti chybám (duplikát / triplikát) a kontroly protokolů (parita rozhraní, zarovnání adres, počet úderů)

- Ověření funkční bezpečnosti , spuštění kampaně o chybách, včetně vložení chyb do návrhu a ověření, že bezpečnostní mechanismus reaguje vhodným způsobem na chyby, které jsou považovány za kryté.

Společnosti

Staré firmy

Tržní kapitalizace a název společnosti k prosinci 2011:

- 5,77 miliardy USD - Synopsys

- 4,46 miliardy $ - kadence

- 2,33 miliardy USD - Mentor Graphics

- 507 milionů USD - Magma Design Automation ; Společnost Synopsys získala společnost Magma v únoru 2012

- 6,44 miliardy NT $ - SpringSoft ; Společnost Synopsys získala společnost SpringSoft v srpnu 2012

- 11,95 miliardy ¥ - Zuken Inc.

Poznámka: EEsof by pravděpodobně měl být na tomto seznamu, ale nemá tržní limit, protože je divizí EDA společnosti Keysight .

Akvizice

Mnoho společností EDA získává malé společnosti se softwarem nebo jinou technologií, kterou lze přizpůsobit jejich hlavní činnosti. Většina lídrů na trhu je sloučením mnoha menších společností a tomuto trendu napomáhá tendence softwarových společností navrhovat nástroje jako příslušenství, které přirozeně zapadá do sady programů větších prodejců na digitálních obvodech ; mnoho nových nástrojů zahrnuje analogový design a smíšené systémy. To se děje kvůli trendu umístit celé elektronické systémy na jeden čip .

Viz také

- Počítačem podporovaný design (CAD)

- Návrh obvodu

- Databáze EDA

- Signoff (automatizace elektronického designu)

- Porovnání softwaru EDA

- Platformový design

Reference

- Poznámky

- http://www.staticfreesoft.com/documentsTextbook.html Počítačové pomůcky pro návrh VLSI od Stevena M. Rubina

- Základy návrhu rozvržení pro elektronické obvody , Lienig, Scheible, Springer, doi : 10.1007/978-3-030-39284-0 ISBN 978-3-030-39284-0 , 2020

- VLSI Physical Design: From Graph Partitioning to Timing Closure , Kahng, Lienig, Markov and Hu, doi : 10.1007/978-90-481-9591-6 ISBN 978-90-481-9590-9 , 2011

- Elektronická příručka automatizace designu pro integrované obvody , Lavagno, Martin a Scheffer, ISBN 0-8493-3096-3 , 2006

- The Electronic Design Automation Handbook , Dirk Jansen et al., Kluwer Academic Publishers, ISBN 1-4020-7502-2 , 2003, k dispozici také v němčině ISBN 3-446-21288-4 (2005)

- Kombinatorické algoritmy pro rozvržení integrovaných obvodů , Thomas Lengauer, ISBN 3-519-02110-2 , Teubner Verlag, 1997.