Intel 8051 - Intel 8051

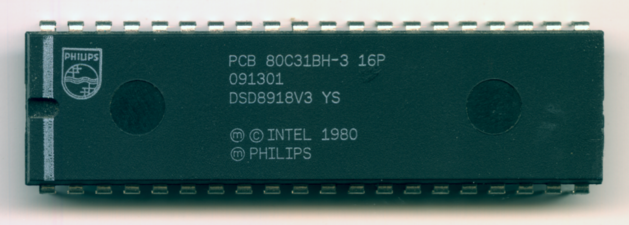

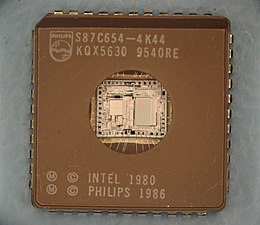

Mikrokontrolér Intel P8051

|

Intel MCS-51 (běžně nazývaný 8051 ) je jednočipový mikrokontrolér (MCU) řady od Intel v roce 1980 pro použití ve vestavěných systémů . Architektem instrukční sady Intel MCS-51 byl John H. Wharton . Původní verze společnosti Intel byly populární v osmdesátých a na začátku devadesátých let a rozšířené binární kompatibilní deriváty zůstávají populární i dnes. Je to příklad složitého počítače s instrukční sadou (ale také s některými funkcemi architektur RISC , jako je velká sada registrů a okna registrů ) a má oddělené paměťové prostory pro programové instrukce a data.

Původní řada MCS-51 společnosti Intel byla vyvinuta pomocí technologie N-type metal-oxid-semiconductor ( NMOS ) jako její předchůdce Intel MCS-48 , ale novější verze označené písmenem C v názvu (např. 80C51) používají doplňkový kov- technologie oxid -polovodič ( CMOS ) a spotřebovávají méně energie než jejich předchůdci NMOS. Díky tomu byly vhodnější pro zařízení napájená bateriemi.

Rodina pokračovala v roce 1996 vylepšenou 8bitovou MCS-151 a 8/ 16 / 32bitovou rodinou MCS-251 binárních kompatibilních mikrokontrolérů. Zatímco Intel již nevyrábí rodinu MCS-51, MCS-151 a MCS-251, vylepšené binární kompatibilní deriváty vyrobené mnoha prodejci jsou dnes stále populární. Některé deriváty integrují procesor digitálního signálu (DSP). Kromě těchto fyzických zařízení nabízí několik společností také deriváty MCS-51 jako IP jádra pro použití v provedeních programovatelných hradlových polí (FPGA) nebo integrovaných obvodů specifických pro aplikace (ASIC).

Důležité funkce a aplikace

Architektura 8051 poskytuje mnoho funkcí ( centrální procesorová jednotka (CPU), paměť s libovolným přístupem (RAM), paměť jen pro čtení (ROM), porty vstup/výstup (I/O), sériový port, řízení přerušení , časovače ) v jednom balíček :

- 8- bit aritmetickou logickou jednotku (ALU) a akumulátor , 8-bitových registrů (jedna 16-bit registru pomocí speciálních tahů instrukcí ), 8-bit datovou sběrnici a 2 x 16-bitové adresy autobusy , programový čítač , ukazatel dat a související 8/11/16bitové operace; jde tedy hlavně o 8bitový mikrokontrolér

- Booleovský procesor se 17 instrukcemi, 1bitový akumulátor, 32 registrů (4 bitové adresovatelné 8bitové) a až 144 speciálních 1bitově adresovatelných proměnných RAM (18bitově adresovatelných 8bitových)

- Násobte , dělejte a porovnávejte pokyny

- Čtyři rychle přepínatelné banky registrů po osmi registrech ( mapováno v paměti )

- Rychlé přerušení s volitelným přepínáním bank registrů

- Přerušení a vlákna s volitelnou prioritou

- 128 nebo 256 bajtů RAM na čipu (IRAM)

- Duální 16bitová adresová sběrnice ; má přístup k 2 × 2 16 paměťovým místům: 64 kB (65 536 míst), každé z ROM (PMEM) a externí RAM (XRAM), pomocí dvou paměťových sběrnic v harvardské architektuře .

- ROM na čipu (není součástí 803x variant)

- Čtyři 8bitové obousměrné vstupní/výstupní porty, bitově adresovatelné

- UART ( sériový port )

- Dva 16bitové čítače/ časovače

- Úsporný režim (u některých derivátů)

Jednou z vlastností jádra 8051 je zahrnutí booleovského procesoru, který umožňuje provádět logické operace na úrovni bitů přímo a efektivně na vybraných interních registrech , portech a vybraných umístěních RAM . Další funkcí je zahrnutí čtyř sad bankovních volitelných pracovních registrů, které výrazně zkracují čas potřebný k provedení kontextových přepínačů pro vstup a opuštění rutin služby přerušení . Pomocí jedné instrukce může 8051 přepínat banky registrů, čímž se vyhnete časově náročnému přenosu kritických registrů do RAM.

Jakmile je nakonfigurován UART a v případě potřeby časovač, programátor potřebuje pouze napsat jednoduchou rutinu přerušení, aby znovu naplnil posuvný registr odesílání, kdykoli je poslední bit posunut pomocí UART a/nebo vyprázdnil celý posuvný registr příjmu (kopie data někde jinde). Hlavní program pak provádí sériová čtení a zápisy jednoduše čtením a zapisováním 8bitových dat do zásobníků.

Derivační funkce

Od roku 2013 stále vyvíjí nové deriváty mnoho hlavních výrobců čipů a hlavní dodavatelé kompilátorů, jako jsou IAR Systems , Keil a Altium Tasking, průběžně vydávají aktualizace.

Mikrokontroléry založené na MCS-51 obvykle obsahují jeden nebo dva UARTy , dva nebo tři časovače, 128 nebo 256 bytů interní datové RAM (z toho 16 bytů je bitově adresovatelných), až 128 bytů I/O , 512 bytů až 64 KB interní programové paměti a někdy i množství rozšířené datové paměti RAM (ERAM) umístěné ve vnějším datovém prostoru. Externí RAM a ROM sdílejí sběrnice dat a adres. Původní jádro 8051 běželo při 12 hodinových cyklech na jeden strojový cyklus, přičemž většina instrukcí byla provedena v jednom nebo dvou strojových cyklech. S hodinovou frekvencí 12 MHz mohl 8051 vykonat 1 milion jednokruhových instrukcí za sekundu nebo 500 000 dvoucyklových instrukcí za sekundu. Nyní se běžně používá vylepšených 8051 jader, která běží na šesti, čtyřech, dvou nebo dokonce na jednom taktu na jeden cyklus stroje (označováno „1T“) a mají taktovací frekvence až 100 MHz, a jsou tedy schopny ještě většího počtu instrukce za sekundu. Všechna Silicon Labs , některé Dallas (nyní součást Maxim Integrated ) a několik zařízení Atmel (nyní součást Microchip ) mají jednocyklová jádra .

Varianty 8051 mohou zahrnovat vestavěné resetovací časovače s detekcí zhasnutí, oscilátory na čipu, programovatelnou paměť programu Flash ROM , vestavěnou externí RAM, extra interní úložiště programů, kód zavaděče v ROM, energeticky nezávislé úložiště EEPROM , I 2 C , SPI a USB hostitelská rozhraní, sběrnice CAN nebo LIN , rádiové moduly ZigBee nebo Bluetooth , generátory PWM , analogové komparátory , převodníky analogových na digitální a digitální na analogové , RTC , přídavné čítače a časovače, v -zařízení pro ladění obvodů , více zdrojů přerušení, extra režimy úspory energie, více/méně paralelních portů atd. Intel vyrobil maskou programovanou verzi, 8052AH-BASIC, s překladačem BASIC v ROM, schopný spouštět uživatelské programy načtené do RAM.

Mikrokontroléry na bázi MCS-51 byly přizpůsobeny extrémním prostředím. Příklady vysokoteplotních variant jsou řada Tekmos TK8H51 pro −40 ° C až +250 ° C nebo Honeywell HT83C51 pro −55 ° C až +225 ° C (s provozem až 1 rok při +300 ° C). K dispozici jsou radionuklidové mikrokontroléry MCS-51 pro použití v kosmických lodích; například od Cobham (dříve Aeroflex ) jako UT69RH051 nebo NIIET jako 1830VE32 ( ruské : 1830ВЕ32 ).

V některých technických školách je mikrokontrolér 8051 používán v úvodních kurzech mikrokontroléru.

Konvence pojmenování rodin

8051 je původní název společnosti Intel se 4 kB ROM a 128 bajty RAM. Varianty začínající na 87 mají uživatelsky programovatelnou EPROM, někdy vymazatelnou UV. Varianty s C jako třetím znakem jsou nějaké CMOS . 8031 a 8032 jsou verze bez paměti ROM se 128 a 256 bajty RAM. Poslední číslice může udávat velikost paměti, např. 8052 s 8 KB ROM, 87C54 16 KB EPROM a 87C58 s 32 KB EPROM, vše s 256 bajty RAM.

Architektura paměti

MCS-51 má čtyři různé typy paměti: interní RAM, speciální funkční registry, programovou paměť a externí datovou paměť. Pro efektivní přístup k těmto kompilátorům využívají až 7 typů definic paměti: interní RAM, jednobitový přístup k interní RAM, speciální funkční registry, jednobitový přístup k vybraným (dělitelným 8) speciální funkční registry, RAM programu, externí RAM přístup pomocí registru nepřímý přístup, pomocí jednoho ze standardních 8bitových registrů, a registrovat nepřímý externí přístup RAM pomocí 16bitového registru nepřímého přístupu.

Instrukční sada 8051 je navržena jako Harvardská architektura se segregovanou pamětí (data a instrukce); může spouštět pouze kód načtený z paměti programu a nemá žádné pokyny k zápisu do paměti programu. Sběrnice opouštějící IC má však jedinou adresu a datovou cestu a silně připomíná sběrnici architektury Von Neumann .

Většina systémů 8051 respektuje sadu instrukcí a ke stahování nových spustitelných programů, např. Ve flash paměti, vyžaduje přizpůsobené funkce.

Interní RAM

Interní paměť RAM (IRAM) má 8bitový adresní prostor využívající adresy 0 až 0xFF. IRAM od 0x00 do 0x7F obsahuje 128 přímo adresovatelných 1bajtových registrů, ke kterým lze přistupovat pomocí 8bitové absolutní adresy, která je součástí instrukce. Alternativně lze k IRAM přistupovat nepřímo: adresa je načtena do R0 nebo R1 a k paměti je přistupováno pomocí syntaxe @R0 nebo @R1, nebo jako paměť zásobníku pomocí ukazatele zásobníku SP, s operacemi PUSH a POP; a *CALL a RET operace.

Původní 8051 má pouze 128 bajtů IRAM. 8052 přidal IRAM od 0x80 do 0xFF, ke kterému lze přistupovat pouze nepřímo (např. Pro použití jako prostor zásobníku). Většina klonů 8051 má také celých 256 bajtů IRAM.

Přímé přístupy k adresám IRAM 80-FF jsou místo toho mapovány na speciální funkční registry (SFR), kde jsou umístěny akumulátory A, B, přenosový bit C a další speciální registry pro řízení, stav atd.

Registry speciálních funkcí

Registry speciálních funkcí (SFR) jsou umístěny ve stejném adresním prostoru jako IRAM, na adresách 0x80 až 0xFF, a je k nim přístup přímo pomocí stejných pokynů jako pro spodní polovinu IRAM. Nelze k nim přistupovat nepřímo přes @R0 nebo @R1 nebo pomocí ukazatele zásobníku SP; nepřímý přístup k těmto adresám bude místo toho přistupovat do druhé poloviny IRAM.

Registry speciální funkce (SFR) zahrnují samotné akumulátory A (nebo ACC, u E0) a B (u F0) a stavové slovo programu (nebo PSW, u D0) a také 16bitový datový ukazatel DPTR (při 82, jako DPL a 83 jako DPH). Kromě nich malé jádro dalších speciálních funkčních registrů - včetně přerušení umožňujícího IE na A8 a prioritní IP přerušení na B8; I/O porty P0 (80), P1 (90), P2 (A0), P3 (B0); sériový I/O řídicí SCON (98) a vyrovnávací paměť SBUF (99); registr řízení CPU/napájení PCON (87); a registry pro časovače 0 a 1 (TCON na 88) a provozní režim (TMOD na 89), 16bitový časovač 0 (TL0 na 8A, TH0 na 8C) a časovač 1 (TL1 na 8B, TH1 na 8D) - jsou přítomny ve všech verzích 8051. Ostatní adresy jsou závislé na verzi; zejména registry časovače 2 pro 8052: řídicí registr T2CON (na C8), 16bitové zachycení/západka (RCAP2L na CA, RCAP2H na CB) a časovač 2 (TL2 na CC a TH2 na CD), jsou není součástí 8051.

Zaregistrujte okna

32 bajtů v IRAM od 0x00–0x1F obsahuje místo pro čtyři osmibajtová registrační okna , do kterých 8 registrů mapuje R0 – R7. Aktuálně aktivní okno je určeno dvoubitovou adresou obsaženou ve stavovém slově programu.

Bitové registry

16 bajtů (128 bitů) na místech IRAM 0x20–0x2F obsahuje prostor pro 128 1bitových registrů, které jsou samostatně adresovatelné jako bitové registry 00-7F.

Zbývající bitové registry, adresované jako 80-FF, jsou mapovány na 16 speciálních funkčních registrů 80, 88, 90, 98, ..., F0 a F8 (ty, jejichž adresy jsou násobky 8), a proto obsahují bity obsahující akumulátory A, B a stavové slovo programu PSW. Adresa okna registru, což jsou bity 3 a 4 na PSW, je sama adresovatelná jako bitové registry D3 respektive D4; zatímco přenosový bit C (nebo CY), na bit 7 PSW, je adresovatelný jako bitový registr D7.

Programová paměť

Programová paměť (PMEM, i když je při používání méně běžná než IRAM a XRAM) má až 64 kB paměti jen pro čtení, počínaje adresou 0 v samostatném adresním prostoru. V závislosti na konkrétním modelu použitého čipu může být čip zapnutý nebo vypnutý. Programová paměť je pouze pro čtení, ačkoli některé varianty 8051 používají flash paměť na čipu a poskytují způsob přeprogramování paměti v systému nebo v aplikaci.

Kromě kódu je možné do paměti programu ukládat data jen pro čtení, jako jsou vyhledávací tabulky , načtená podle pokynů nebo . Adresa se vypočítá jako součet 8bitového akumulátoru a 16bitového registru (PC nebo DPTR).

MOVC A,@A+DPTRMOVC A,@A+PC

Speciální pokyny pro přeskakování a volání ( AJMPa ACALL) mírně zmenšují velikost kódu, který přistupuje k místní (ve stejné 2 kB) paměti programu.

Když je vyžadován kód větší než 64 kB, společný systém přepne banku kódu, přičemž univerzální I/O vybere bity horní adresy. Některé kompilátory 8051 zajišťují automatický přístup k stránkovanému kódu. V těchto systémech jsou vektory přerušení a stránkovací tabulka umístěny v prvních 32 kB kódu a jsou vždy rezidentní.

Externí datová paměť

Externí paměť dat (XRAM) je třetím adresním prostorem, který také začíná na adrese 0 a umožňuje 16 bitů adresního prostoru. Může být také na či mimo čip; to, co dělá to „externí“, je to, že k tomu musí být přístup pomocí MOVXinstrukce (přesunout externí). Mnoho variant 8051 obsahuje standardních 256 bajtů IRAM plus několik kilobajtů XRAM na čipu.

Prvních 256 bajtů XRAM lze přistupovat pomocí , , a instrukce. K plným 64 kB lze přistupovat pomocí a . 16bitová adresa vyžaduje, aby programátor zavedl 16bitový indexový registr. Z tohoto důvodu jsou RAM přístupy se 16bitovými adresami podstatně pomalejší.

MOVX A,@R0MOVX A,@R1MOVX @R0,AMOVX @R1,AMOVX A,@DPTRMOVX @DPTR,A

Některé CPU umožňují, aby 8bitová nepřímá adresa používala jakýkoli 8bitový registr obecného účelu.

Aby bylo možné tuto funkci používat, některé mikrokontroléry kompatibilní s 8051 s interní pamětí RAM větší než 256 bajtů nebo nemožností přístupu k externí paměti RAM přistupují k vnitřní paměti RAM, jako by byly externí, a mají speciální registr funkcí (např. PDATA), který jim umožňuje pro nastavení horní adresy stránky o 256 bajtech. Toto emuluje režim MCS8051, který může stránkovat horní bajt adresy RAM nastavením obecných I/O pinů.

Když je vyžadována paměť RAM větší než 64 kB, běžný systém provede přepnutí banky RAM, přičemž obecné I/O vybírá bity horní adresy. Některé kompilátory 8051 zajišťují automatický přístup k stránkovaným datům.

Registry

Jediným registrem na 8051, který není mapován do paměti, je 16bitový čítač programů (PC). Toto určuje adresu další instrukce, která se má provést. Relativní větve poskytují 8bitový podepsaný offset, který je přidán do PC.

K osmi obecným registrům R0 – R7 lze přistupovat s pokyny o jeden bajt kratší než ostatní. Jsou mapovány na IRAM mezi 0x00 a 0x1F. V daném čase je použito pouze osm bajtů tohoto rozsahu, určených dvěma bity výběru banky v PSW.

Následuje částečný seznam registrů 8051, které jsou mapovány v paměti do prostoru registrů speciální funkce:

- Ukazatel zásobníku, SP (0x81)

- Jedná se o 8bitový registr používaný podprogramovými pokyny pro volání a návrat. Stoh roste vzhůru; SP se zvýší před tlačením a sníží po vyskočení hodnoty.

- Datový ukazatel, DP (0x82–83)

- Toto je 16bitový registr, který se používá pro přístup k PMEM a XRAM.

- Programové stavové slovo, PSW (0xD0)

- Obsahuje důležité stavové příznaky podle bitového čísla:

- Parita, P. Udává paritu ( XOR bitů) akumulátoru, A.

- Definováno uživatelem, UD. Lze je číst a zapisovat pomocí softwaru; není jinak ovlivněn hardwarem.

- Vlajka přetečení , OV. Nastavit, když přidání vytvoří podepsané přetečení.

- Zaregistrujte se, vyberte 0, RS0. Bit nízkého řádu registrační banky. Nastavte, když se používají banky 0x08 nebo 0x18.

- Zaregistrujte se, vyberte 1, RS1. Bit vysokého řádu registrační banky. Nastavte, když se používají banky 0x10 nebo 0x18.

- Vlajka 0, F0. Lze je číst a zapisovat pomocí softwaru; není jinak ovlivněn hardwarem.

- Pomocné nošení , AC. Nastavte, když sčítání vytvoří přenos z bitu 3 do bitu 4.

- Carry bit , C. Často se používá jako obecný registr pro bitové výpočty nebo „booleovský akumulátor“.

- Akumulátor, A (0xE0)

- Tento registr používá většina pokynů.

- B registr (0xF0)

- Toto se používá jako rozšíření akumulátoru pro pokyny pro násobení a dělení.

256 jednotlivých bitů je přímo adresovatelných. Jedná se o 16 umístění IRAM od 0x20–0x2F a 16 registrů speciálních funkcí 0x80, 0x88, 0x90, ..., 0xF8. Jakýkoli bit těchto bajtů může být přímo přístupný řadou logických operací a podmíněných větví.

Všimněte si, že PSW neobsahuje společné záporné (N) nebo nulové (Z) příznaky . U prvního lze nejvýznamnější bit akumulátoru adresovat přímo, protože jde o bitově adresovatelný SFR. U posledně jmenovaných existují explicitní pokyny ke skoku, zda je akumulátor nulový nebo ne. K dispozici je také operace porovnávání a skoku o dvou operandech.

Paritní bit (P) se často používá k implementaci sériových režimů, které zahrnují paritu. Aby to podpořily, standardní MCS51 UART mohly odeslat 9 bitů.

Mikroarchitektura

Mikroarchitektura Intel MCS8051 je proprietární, ale publikované funkce naznačují, jak funguje. Jedná se o vícecyklový procesor . MCS8051 použil pro většinu instrukcí 12 hodinových cyklů. Počet cyklů na instrukci (větší než 8) naznačuje, že má jednobitovou aritmetickou logickou jednotku, která zpracovává svá 8bitová data po jednom bitu. To by také mohlo vysvětlovat, proč může ekonomicky poskytovat jednobitové instrukce. Relativně velký počet cyklů také naznačuje, že využívá pouze jednu hranu svých hodin. (Mnoho vícekolových počítačů provozuje svoji logiku na obou hranách.)

Mnoho instrukcí využívá akumulátor. Protože má akumulátor, může potřebovat akumulátor, aby poskytl jeden vstup ze dvou vstupů potřebných jeho aritmetickou logickou jednotkou. To znamená, že má pouze jednu interní sběrnici (ekonomický design), nikoli více sběrnic z dvojitého portovaného registru, které by mohlo napájet obě strany ALU. Aby se snížily náklady, namísto používání multiplexerů může zařízení zapínat a vypínat sběrnici pomocí třístavových logických zařízení. Třístavová sériová sběrnice by také umožnila ekonomický jednobitový multiplexer pro její systém registru přepínaného bankou.

Naproti tomu většina kompatibilních počítačů provádí instrukce v jednom až třech cyklech, s výjimkou instrukcí pro násobení a dělení. Mnohem vyšší rychlost je hlavním důvodem, proč tyto nahradily MCS8051 ve většině aplikací. Rychlost naznačuje, že tyto mají osmibitové interní sběrnice a aritmetické logické jednotky.

Každé přerušení má čtyři priority. V rámci každé priority mají přerušení zařízení pevnou prioritu. Zdá se tedy, že řadič přerušení upřednostňuje přerušení čtyřmi sekvenčními řetězci bran, přičemž každé přerušení má bránu v každém prioritním řetězci.

Instrukční sada

Pokyny jsou všechny 1 až 3 bajty dlouhé, skládající se z počátečního bajtu operačního kódu, za nímž následují až 2 bajty operandů.

1 / 4 z operačního kódu bajtů, x 0- x 3 , se používají pro nepravidelné operačních kódů.

3 / 4 z operačního kódu bajtů, x 4- x F , jsou přiřazeny k 16 základních ALU instrukce s 12 možnými operandy. Nejméně významná okuska operačního kódu vybere primární operand následovně:

- x 8– x F : Přímá registrace, R0 – R7.

- x 6– x 7 : Nepřímá registrace, @R0 nebo @R1.

- x 5 : Přímá paměť, následující bajt určuje umístění IRAM nebo SFR.

-

x 4 : Okamžitý, následující bajt určuje 8bitovou konstantu. Když je operandem destinace (,) nebo operace již obsahuje okamžitý zdroj (,), místo toho určuje, že se použije akumulátor.

INC operandDEC operandMOV operand,#dataCJNE operand,#data,offset

Nejvýznamnější nibble specifikuje operaci následovně. Ne všechny podporují všechny režimy adresování; zejména okamžitý režim není k dispozici, když je zapsán primární operand. Instrukční mnemotechnické pomůcky používají cíl , pořadí operandů zdroje .

- 0 y :

INC operand - Zvyšte zadaný operand. Okamžitý režim (opcode 0x04) specifikuje akumulátor, .

INC A - 1 y :

DEC operand - Snižte zadaný operand. Okamžitý režim (opcode 0x14) specifikuje akumulátor, .

DEC A - 2 roky :

ADD A,operand - Přidejte operand do akumulátoru A. Operační kód 0x23 ( „otočit doleva“, ale ve skutečnosti posun doleva ) lze považovat za .

RL AADD A,A - 3 roky :

ADDC A,operand - Přidejte operand plus bit C do akumulátoru. Operační kód 0x33 ( otočit doleva přenášením) lze považovat za .

RLC AADDC A,A - 4 roky :

ORL A,operand - Logický NEBO operand do akumulátoru. Dvě formy cílové paměti této operace a jsou specifikovány operačními kódy 0x43 a 0x42.

ORL address,#dataORL address,A - 5 y :

ANL A,operand - Logické A operand do akumulátoru. Dvě formy cílové paměti této operace a jsou specifikovány operačními kódy 0x53 a 0x52.

ANL address,#dataANL address,A - 6 y :

XRL A,operand - Logická exkluzivita-NEBO operand do akumulátoru. Dvě formy cílové paměti této operace a jsou specifikovány operačními kódy 0x63 a 0x62.

XRL address,#dataXRL address,A - 7 y :

MOV operand,#data - Okamžitě se přesuňte na operand. Okamžitý režim (opcode 0x74) specifikuje akumulátor, .

MOV A,#data - 8 y :

MOV address,operand - Přesuňte hodnotu do registru IRAM nebo SFR. Okamžitý režim (opcode 0x84) se pro tuto operaci nepoužívá, protože duplikuje opcode 0x75.

- 9 y :

SUBB A,operand - Odečtěte operand od akumulátoru. Tato operace si půjčuje a bez půjčky není možné odečíst .

- A y :

MOV operand,address - Přesuňte hodnotu z registru IRAM nebo SFR. Okamžitý režim (operační kód 0xA4) se nepoužívá, protože bezprostředně slouží pouze jako zdroje. Režim přímé paměti (opcode 0xA5) se nepoužívá, protože duplikuje 0x85.

- B y :

CJNE operand,#data,offset - Porovnejte operand s okamžitým

#dataa přeskočte na offset PC +, pokud není stejný. Okamžitá a paměť přímé režimy (opcodes 0xB4 a 0xB5) porovnat operand proti akumulátoru . Všimněte si, že neexistuje žádné srovnání a skok, pokud se rovná instrukce .CJNE A,operand,offsetCJE - C y :

XCH A,operand - Vyměňte akumulátor a operand. Okamžitý režim (operační kód 0xC4) se pro tuto operaci nepoužívá.

- D y :

DJNZ operand,offset - Pokud je výsledek nenulový, snižte operand a přejděte na offset PC + . Okamžitý režim (operační kód 0xD4) a nepřímý režim registru (0xD6, 0xD7) se nepoužívají.

- E y :

MOV A,operand - Přesuňte operand do akumulátoru. Okamžitý režim se pro tuto operaci nepoužívá (opcode 0xE4), stejně jako duplikáty opcode 0x74.

- F y :

MOV operand,A - Přesuňte akumulátor na operand. Okamžitý režim (opcode 0xF4) se nepoužívá, protože by neměl žádný účinek.

Pouze ADD, ADDCa SUBBpokyny stanovené PSW vlajky. Tyto INC, DECa logické instrukce ne. Tyto CJNEinstrukce modifikuje C bit pouze na půjčit, že výsledky z operand1 - operand2 .

Nepravidelné instrukce obsahují 64 operačních kódů, které mají omezenější režimy adresování, a několik operačních kódů zachycených z neaplikovatelných režimů v běžných instrukcích.

| Opcode | x 0 | x 1 | x 2 | x 3 | x 4 |

|---|---|---|---|---|---|

| 0 r |

NOP

|

LJMP addr16 |

RR A (otočit doprava) |

INC A

|

|

| 1 y |

JBC bit,offset (skok, pokud je bit nastaven s vymazáním)

|

LCALL addr16 |

RRC A (otočit doprava přes nošení) |

DEC A

|

|

| 2 r |

JB bit,offset (skok, pokud je bit nastaven)

|

RET |

RL A (otočit doleva) |

ADD A,#data

|

|

| 3 r |

JNB bit,offset (skok, pokud je bit jasný)

|

RETI |

RLC A (otočit doleva skrz přenášení) |

ADDC A,#data

|

|

| 4 r |

JC offset (skok, pokud je přenášen)

|

ORL address,A |

ORL address,#data |

ORL A,#data

|

|

| 5 y |

JNC offset (vyskoč, pokud neseš volný)

|

ANL address,A |

ANL address,#data |

ANL A,#data

|

|

| 6 r |

JZ offset (skok, pokud nula)

|

XRL address,A |

XRL address,#data |

XRL A,#data

|

|

| 7 y |

JNZ offset (skok nenulový)

|

ORL C,bit |

JMP @A+DPTR |

MOV A,#data

|

|

| 8 r |

SJMP offset (krátký skok)

|

ANL C,bit |

MOVC A,@A+PC |

DIV AB

|

|

| 9 y |

MOV DPTR,#data16

|

MOV bit,C |

MOVC A,@A+DPTR |

SUBB A,#data

|

|

| A y |

ORL C,/bit

|

MOV C,bit |

INC DPTR |

MUL AB

|

|

| B y |

ANL C,/bit

|

CPL bit |

CPL C |

CJNE A,#data,offset

|

|

| C y |

PUSH address

|

CLR bit |

CLR C |

SWAP A

|

|

| D y |

POP address

|

SETB bit |

SETB C |

DA A (desetinná úprava)

|

|

| E y |

MOVX A,@DPTR

|

MOVX A,@R0 |

MOVX A,@R1 |

CLR A

|

|

| F y |

MOVX @DPTR,A

|

MOVX @R0,A |

MOVX @R1,A |

CPL A

|

- A5

- Nepoužitý

- B5

CJNE A,address,offset- D6–7

-

XCHD A,@R0–1vyměňovat okusování operandů nízkého řádu.

SJMP(Krátký skok) operační kód trvá podepsanou relativní offset byte operandů a kontrolovat tam transfery ve vztahu k adresu následujícího návodu. K AJMP/ ACALLopcodes kombinují tří nejvýznamnějších bitů operačního kódu bajt s tímto bytem zadat 11-bitový cíl, který se používá jako náhrada 11 spodní bity PC registru (top 5 bity PC registru zůstanou beze změny). U větších adres pokyny LJMPa LCALLumožňují 16bitové určení.

Jedním z důvodů popularity 8051 je rozsah operací s jednotlivými bity. Bity jsou vždy určeny absolutními adresami; neexistuje žádné nepřímé nebo indexované adresování registrů. Pokyny, které fungují na jednotlivých bitech, jsou:

-

SETB bit, , : Set, vymazat nebo doplnit zadaný bitCLR bitCPL bit -

JB bit,offset: Skočte, pokud je bit nastaven -

JNB bit,offset: Skočte, pokud je to trochu jasné -

JBC bit,offset: Skočte, pokud je bit nastaven, a vymažte bit -

MOV C,bit, : Přesuňte zadaný bit na přenosový bit nebo naopakMOV bit,C -

ORL C,bit, : Nebo bit (nebo jeho doplněk) k přenosovému bituORL C,/bit -

ANL C,bit, : A bit (nebo jeho doplněk) k přenosovému bituANL C,/bit

Ve formuláři je zapsán bitový operand address.number. Vzhledem k tomu, carry flag je bit 7 programovém stavovém slovu bit adresovatelné se , a pokyny jsou kratší ekvivalenty , a .

SETB CCLR CCPL CSETB PSW.7CLR PSW.7CPL PSW.7

Ačkoli většina pokynů vyžaduje, aby jeden operand byl akumulátor nebo okamžitá konstanta, operační kód 0x85 funguje MOVpřímo mezi dvěma interními umístěními RAM.

Programování

Pro 8051 existují různé kompilátory na vysoké úrovni programovacího jazyka. Pro 8051 je k dispozici několik kompilátorů C , z nichž většina umožňuje programátorovi určit, kde by měla být každá proměnná uložena v jejích šesti typech paměti, a poskytnout přístup k specifickému hardwaru 8051. funkce, jako jsou banky více registrů a pokyny pro manipulaci s bitem. Existuje mnoho komerčních kompilátorů C. Small Device C Compiler (SDCC) je populární open source C překladač. Pro 8051 jsou k dispozici i další jazyky na vysoké úrovni, jako je C ++ , Forth , BASIC , Object Pascal , Pascal , PL/M a Modula-2 , ale používají se méně často než C a assembly .

Protože všechny IRAM, XRAM a PMEM (pouze pro čtení) mají adresu 0, kompilátory C pro architekturu 8051 poskytují pragmata specifická pro kompilátory nebo jiná rozšíření, která indikují, kde by měla být uložena konkrétní část dat (tj. Konstanty v PMEM nebo proměnné vyžadující rychlý přístup v IRAM). Vzhledem k tomu, že data mohou být v jednom ze tří paměťových prostorů, je obvykle k dispozici mechanismus umožňující určit, na kterou paměť ukazatel odkazuje, a to buď omezením typu ukazatele tak, aby zahrnoval paměťový prostor, nebo uložením metadat s ukazatelem.

Související procesory

Intel přerušil svou produktovou řadu MCS-51 v březnu 2007; od jiných prodejců je však pravidelně přidáváno mnoho vylepšených produktů 8051 nebo silikonového duševního vlastnictví .

Předchůdce 8051, 8048 , byl použit v klávesnici prvního počítače IBM PC , kde převáděl stisknutí kláves do proudu sériových dat, který je odesílán do hlavní jednotky počítače. Intel 8049 sloužil podobnou roli v Sinclair QL . 8048 a deriváty se dodnes používají pro základní modelové klávesnice.

8031 byla snížená verze původního 8051, který měl žádné vnitřní paměti programu ( Read-Only Memory , ROM). Aby bylo možné tento čip použít, musela být přidána externí ROM obsahující program, který 8031 načte a spustí. Čip 8051 by mohl být prodáván jako 8031 bez ROM, protože interní ROM 8051 je deaktivována normálním stavem kolíku EA v provedení založeném na 8031. Prodejce může prodat 8051 jako 8031 z libovolného počtu důvodů, jako je chybný kód v paměti ROM 8051 nebo jednoduše nadměrná nabídka 8051s a nedostatečná nabídka 8031s.

8052 byla vylepšená verze původního 8051 to představovalo 256 bytů vnitřní paměti RAM namísto 128 bytů, 8 KB ROM namísto 4 KB a třetí 16-bitový časovač. Tyto funkce obsahuje většina moderních mikrokontrolérů kompatibilních s 8051.

8032 měli tyto stejné vlastnosti jako 8052 s výjimkou postrádala programové paměti interní ROM.

8751 byl 8051 s 4 KB EPROM místo 4 kB ROM. Byly identické až na typ energeticky nezávislé paměti. Tato část byla k dispozici v keramickém obalu s čirým křemenným okénkem přes horní část matrice, takže k vymazání EPROM bylo možné použít UV světlo . Související části jsou: 8752 měl 8 KB EPROM, 8754 měl 16 KB EPROM, 8758 měl 32 KB EPROM.

80C537 (ROM-less) a 80C517 (8 KB ROM) jsou CMOS verze, určené pro automobilový průmysl . Vylepšení většinou zahrnují nové a vylepšené periferie. 80C5x7 má mechanismy bezpečné proti selhání, zařízení pro zpracování analogového signálu, vylepšené možnosti časovače a 32bitovou aritmetickou periferii. Mezi další funkce patří:

- 256bajtová RAM na čipu

- 256 přímo adresovatelných bitů

- Externí programová a datová paměť rozšiřitelná až na 64 kB

- 8bitový A/D převodník s 12 multiplexovanými vstupy

- Aritmetické periferie mohou provádět operace 16 × 16 → 32bitové násobení, 32/16 → 16bitové dělení, 32bitové posuny a 32bitové normalizace

- Osm datových ukazatelů místo jednoho pro nepřímé adresování programu a externí datové paměti

- Rozšířené hlídací zařízení

- Devět I/O portů

- Dvě plně duplexní sériová rozhraní s jednotlivými generátory přenosové rychlosti

- Čtyři prioritní systémy přerušení, 14 vektorů přerušení

- Tři režimy úspory energie

- Druhé zdroje Intel MCS-51

AMD D87C51

OKI M80C31

Philips PCB80C31

Signetics SCN8031

Prodejci derivátů

Více než 20 nezávislých výrobců vyrábí procesory kompatibilní s MCS-51.

Další integrované obvody nebo IP kompatibilní s MCS-51 byly vyvinuty společnostmi Analog Devices , Integral Minsk , Kristall Kyiv a NIIET Voronesh .

Použití jako duševní vlastnictví

Dnes jsou 8051 stále k dispozici jako diskrétní součásti, ale většinou se používají jako křemíková jádra duševního vlastnictví . Tato jádra, která jsou k dispozici ve zdrojovém kódu popisu hardwaru (například VHDL nebo Verilog ) nebo netlistu FPGA , jsou obvykle integrována do vestavěných systémů, od produktů od USB flash disků přes pračky až po komplexní bezdrátové komunikační systémy na čipu . Designéři používají 8051 křemíkových IP jader kvůli menší velikosti a nižšímu výkonu ve srovnání s 32bitovými procesory, jako jsou řady ARM Cortex-M , MIPS a BA22.

Moderní jádra 8051 jsou rychlejší než předchozí zabalené verze. Vylepšení designu zvýšilo výkon 8051 při zachování kompatibility s původní sadou instrukcí MCS 51. Původní Intel 8051 běžel při 12 hodinových cyklech na jeden strojový cyklus a většina instrukcí byla provedena v jednom nebo dvou strojových cyklech. Typický maximální taktovací kmitočet 12 MHz znamenal, že tyto staré 8051 mohly vykonat jeden milion jednokruhových instrukcí nebo 500 000 dvoucyklových instrukcí za sekundu. Naproti tomu vylepšená 8051 křemíková IP jádra nyní běží v jednom taktovacím cyklu na cyklus stroje a mají taktovací frekvence až 450 MHz. To znamená, že procesor kompatibilní s 8051 může nyní vykonávat 450 milionů instrukcí za sekundu.

MCU založené na 8051

- ABOV: Řady MC94F, MC95F, MC96F

- Infineon: XC800

- Maxim Integrated (dříve Dallas): řada DS80 atd.

- Grafika Mentor: M8051EW atd. Určená pro Mentor od SYNTILL8

- Megawin: řady 74, 82, 84, 86, 87 a 89

- Mikročip (dříve Atmel): AT89C51, AT89S51 , AT83C5134 atd.

- NXP: řady NXP700 a NXP900

- Siemens SAB 80532-N

- Měření elektrické energie Silergy : 71M6511, 71M6513, 71M6531, 71M6533, 71M6534, 71M6542, 71M6543 Měření energie SoCs : 78M6631, 78M6618, 78M6613, 78M6612

- Silicon Labs: C8051 série a série EFM8

- Silicon Storage Technology : FlashFlex51 MCU (SST89E52RD2, SST89E54RD2, SST89E58RD2, SST89E516RD2SST89V52RD2, SST89V54RD2, SST89V58RD2, SST89V516RD2)

- STC Micro: STC89C51RC, STC90C51RC, STC90C58AD, STC10F08XE, STC11F60XE, STC12C5410AD, STC12C5202AD, STC12C5A60S2, STC12C5628AD, STC15F100, STC15F204EA, STC15F2K60S2, STC15F4K60S2, STC15F101W, STC15F408AD, STC15W104, STC15W408S, STC15W201S, STC15W408AS, STC15W1K16S a řada STC15W4K56S4

- Rodiny RF SoC společnosti Texas Instruments CC111x, CC24xx a CC25xx

- WCH ( Nanjing Qinheng Microelectronics ): CH551, CH552, CH554, CH546, CH547, CH548, CH558, CH559

Varianty procesoru digitálního signálu (DSP)

Existuje několik variant s přídavným 16bitovým procesorem digitálního signálu (DSP) (například pro kódování/dekódování MP3 nebo Vorbis ) s až 675 miliony instrukcí za sekundu (MIPS) a integrovaným rozhraním USB 2.0 nebo jako duševní vlastnictví.

Vylepšený 8bitový binární kompatibilní mikrokontrolér: řada MCS-151

V roce 1996 Intel oznámil rodinu MCS-151, což je až 6krát rychlejší varianta, plně binární a instrukční sada kompatibilní s 8051. Na rozdíl od 8051 je MCS-151 propojený procesor s 16bitovou interní kódovou sběrnicí a 6x vyšší Rychlost. Řadu MCS-151 společnost Intel také ukončila, ale je široce dostupná v binárních kompatibilních a částečně vylepšených variantách.

8/16/32 bitový binární kompatibilní mikrokontrolér: rodina MCS-251

8/16/32bitový mikrokontrolér 80251 s adresovým prostorem 16 MB ( 24 bitů ) a 6krát rychlejším instrukčním cyklem představila společnost Intel v roce 1996. Může fungovat jako 8bitový 8051, má 24bitové lineární adresování , 8bitová ALU, 8bitové instrukce, 16bitové instrukce, omezená sada 32bitových instrukcí, 16 8bitových registrů, 16 16bitových registrů (8 16bitových registrů, které nesdílejí prostor s žádným 8bitové registry a 8 16bitových registrů, které obsahují 2 8bitové registry na 16bitový registr) a 10 32bitových registrů (2 vyhrazené 32bitové registry a 8 32bitových registrů, které obsahují 2 16bitové registry) bitové registry na 32bitový registr).

Obsahuje rozšířené pokyny - viz také průvodce programátorem - a novější varianty s vyšším výkonem, dostupné také jako duševní vlastnictví (IP). Je to třístupňové potrubí. Řadu MCS-251 společnost Intel také ukončila, ale je široce dostupná v binárních kompatibilních a částečně vylepšených variantách od mnoha výrobců.

Viz také

- DS80C390

- Hitachi HD44780 - LCD ovladač s rozhraním kompatibilním s XRAM

- Intel PL/M-51

- Sada pro návrh systému SDK-51

Reference

Další čtení

- Knihy

- Mazidi; McKinlay; Mazidi (2012). Mikrokontrolér 8051: Systémový přístup . 648 s. ISBN 978-0-13-508044-3.

- Schultz, Thomas (2008). C a 8051 (4. vyd.). 464 s. ISBN 978-0-9783995-0-4.

- Steiner, Craig (2005). Mikrokontrolér 8051/8052: architektura, jazyk sestavy a hardwarové rozhraní . 348 s. ISBN 978-1-58112-459-0.

- Kalkat; Cowan; Parchizadeh (2000). Mikrokontroléry 8051: Hardware, software a aplikace . 329 s. ISBN 978-0-340-67707-0.

- Axelson, leden (1994). Idea knihy o mikrokontroléru: Obvody, programy a aplikace s mikrokontrolérem 8052-BASIC . 277 s. ISBN 978-0-9650819-0-0.

- Payne, William (19. prosince 1990) [1990]. Vestavěný ovladač FORTH pro rodinu 8051 (vázaná kniha). Boston: Academic Press. 528 s. ISBN 978-0-12-547570-9.

- Intel

- Mikrokontrolér MCS-51 Family Uživatelská příručka ; Intel; 1994; číslo publikace 121517.

- Uživatelská příručka MCS-51 Macro Assembler ; Intel; číslo publikace 9800937.

- 8bitové integrované řadiče ; Intel; 1991; číslo publikace 270645-003.

- Příručka mikrokontroléru ; Intel; 1984; číslo publikace 210918-002.

- Mikrokontrolér 8051 Předběžná architektonická specifikace a funkční popis ; Intel; 44 stran; 1980.

externí odkazy

![]() Média související s MCS-51 na Wikimedia Commons

Média související s MCS-51 na Wikimedia Commons