NOR brána - NOR gate

| Vstup | Výstup | |

| A | B | A NOR B |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

NOR gate je digitální logické hradlo , které realizuje logický NOR - se chová podle pravdivostní tabulky na pravé straně. HIGH výstup (1) je výsledkem, pokud jsou oba vstupy do brány LOW (0); pokud je jeden nebo oba vstupy VYSOKÝ (1), bude výsledkem NÍZKÝ výstup (0). NOR je výsledkem negace z OR operátorem. To může také být v některých smyslech považováno za inverzi brány AND . NOR je funkčně kompletní operace - brány NOR lze kombinovat a generovat jakoukoli další logickou funkci. Sdílí tuto vlastnost s bránou NAND . Naproti tomu operátor OR je monotónní, protože může změnit pouze LOW na HIGH, ale ne naopak.

Ve většině implementací obvodů, ale ne ve všech, je negace zdarma - včetně CMOS a TTL . V takových logických rodinách je OR složitější operací; může použít NOR následovaný NOT. Významnou výjimkou jsou některé formy domino logické rodiny.

Původní naváděcí počítač Apollo používal 4 100 integrovaných obvodů (IC), z nichž každý obsahoval pouze dvě 3-vstupní brány NOR.

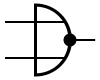

Symboly

Pro brány NOR existují tři symboly: americký (ANSI nebo „vojenský“) symbol a symbol IEC („evropský“ nebo „obdélníkový“), stejně jako zastaralý symbol DIN . Další informace najdete v části Symboly logických bran . Symbol ANSI pro bránu NOR je standardní brána OR s připojenou inverzní bublinou. Bublina označuje, že funkce brány nebo byla obrácena.

|

|

|

| Symbol MIL / ANSI | Symbol IEC | Symbol DIN |

Popis hardwaru a pinout

Brány NOR jsou základní logické brány a jako takové jsou rozpoznávány v integrovaných obvodech TTL a CMOS . Standardní CMOS IC řady 4000 je 4001, který obsahuje čtyři nezávislé brány NOR se dvěma vstupy. Schéma zapojení je následující:

Pinoutový diagram IC 4001 Quad NOR DIP - formát

|

1 Input A1 2 Input B1 3 Output Q1 4 Output Q2 5 Input B2 6 Input A2 7 Vss 8 Input A3 9 Input B3 10 Output Q3 11 Output Q4 12 Input B4 13 Input A4 14 Vdd |

Dostupnost

Tato zařízení jsou k dispozici od většiny výrobců polovodičů, jako jsou Fairchild Semiconductor , Philips nebo Texas Instruments . Ty jsou obvykle k dispozici jak ve formátu DIP průchozí dírou, tak ve formátu SOIC . Datové listy jsou snadno dostupné ve většině databází datových listů .

V oblíbených logických rodinách CMOS a TTL jsou k dispozici brány NOR s až 8 vstupy:

-

CMOS

- 4001: Quad 2-input NOR gate

- 4025: Triple 3-input NOR gate

- 4002: Dvojitá brána NOR se 4 vstupy

- 4078: Jedna brána NOR s 8 vstupy

-

TTL

- 7402: Quad 2-input NOR gate

- 7427: Triple 3-input NOR gate

- 7425: Duální brána NOR se 4 vstupy (se stroboskopem, zastaralá)

- 74260: Dual 5-Input NOR Gate

- 744078: Jedna brána NOR s 8 vstupy

Ve starších rodinách RTL a ECL byly brány NOR účinné a nejčastěji používané.

Implementace

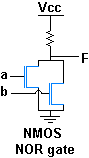

Výše uvedená schémata ukazují konstrukci 2-vstupní brány NOR pomocí logických obvodů NMOS . Pokud je jeden ze vstupů vysoký, zapne se odpovídající N-kanálový MOSFET a výstup je nízký; jinak je výstup vytažen vysoko přes pull-up rezistor .

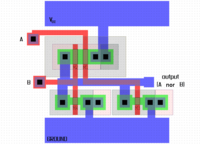

Níže uvedený diagram ukazuje 2vstupovou bránu NOR využívající technologii CMOS . Tyto diody a odpory na vstupy jsou pro ochranu součásti CMOS před poškozením v důsledku elektrostatického výboje (ESD) a nehrají žádnou roli v logické funkce obvodu.

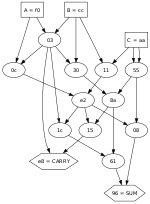

Funkční úplnost

Brána NOR má vlastnost funkční úplnosti , kterou sdílí s bránou NAND. To znamená, že jakoukoli jinou logickou funkci (AND, OR atd.) Lze implementovat pouze pomocí bran NOR. Celý procesor lze vytvořit pouze pomocí bran NOR.

Jako NAND brány jsou také funkčně kompletní, jsou-li k dispozici žádné konkrétní NOR brány, jeden může být vyrobena z NAND brány použitím NAND logiku .

| Požadovaná brána | Stavba NAND |

|---|---|

|

|

Viz také

- A brána

- NEBO brána

- NENÍ brána

- Brána NAND

- XOR brána

- XNOR brána

- Logika NAND

- Booleova algebra (logika)

- Flash paměť

Reference