POWER5 - POWER5

| Obecná informace | |

|---|---|

| Spuštěno | 2004 |

| Navrhl | IBM |

| Výkon | |

| Max. Taktovací frekvence CPU | 1,5 GHz až 2,3 GHz |

| Mezipaměti | |

| Mezipaměť L1 | 32+32 KB/jádro |

| Mezipaměť L2 | 1,875 MB/čip |

| Mezipaměť L3 | 36 MB/čip (mimo čip) |

| Architektura a klasifikace | |

| Min. velikost funkce | 130 nm až 90 nm |

| Instrukční sada | PowerPC 2.02 |

| Fyzické specifikace | |

| Jádra | |

| Dějiny | |

| Předchůdce | VÝKON 4 |

| Nástupce | VÝKON 6 |

| Architektury POWER , PowerPC a Power ISA |

|---|

| NXP (dříve Freescale a Motorola) |

| IBM |

|

| IBM/Nintendo |

| jiný |

| Související odkazy |

| Zrušeno šedou barvou , historické kurzívou |

POWER5 je mikroprocesor vyvinuta a vyrobena IBM . Je to vylepšená verze POWER4 . Hlavními vylepšeními jsou podpora pro simultánní multithreading (SMT) a řadič paměti on-die . POWER5 je dvoujádrový mikroprocesor, přičemž každé jádro podporuje jedno fyzické vlákno a dvě logická vlákna, celkem tedy dvě fyzická vlákna a čtyři logická vlákna.

Dějiny

Technické detaily mikroprocesoru byly poprvé představeny na konferenci Hot Chips v roce 2003 . Úplnější popis byl uveden na fóru Microprocessor Forum 2003 dne 14. října 2003. POWER5 nebyl prodáván otevřeně a byl používán výhradně společností IBM a jejich partnery. Systémy používající mikroprocesoru byla zavedena v roce 2004. POWER5 soutěžil v high-end trhu podnikových serverů, hlavně proti Intel Itanium 2, a v menší míře, Sun Microsystems UltraSPARC IV a Fujitsu SPARC64 V . V roce 2005 byla nahrazena vylepšenou iterací, POWER5+.

Popis

POWER5 je dalším vývojem POWER4 . Přidání obousměrného multithreadingu vyžadovalo duplikaci zpětného zásobníku, čítače programu , vyrovnávací paměti instrukcí, jednotky pro dokončení skupiny a fronty úložiště, takže každé vlákno může mít své vlastní. Většina prostředků, jako jsou soubory registrů a prováděcí jednotky, je sdílena, přestože každé vlákno vidí svou vlastní sadu registrů. POWER5 implementuje simultánní multithreading (SMT), kde jsou prováděna dvě vlákna současně. POWER5 může zakázat SMT pro optimalizaci pro aktuální pracovní zátěž.

Protože je mnoho prostředků, jako jsou soubory registru, sdíleno dvěma vlákny, v mnoha případech se zvyšuje jejich kapacita, aby se kompenzovala ztráta výkonu. Počet celočíselných registrů a registrů s plovoucí desetinnou čárkou se zvýší na 120 z 80 celočíselných a 72 registrů s plovoucí desetinnou čárkou v POWER4. Mezipaměť instrukcí s pohyblivou řádovou čárkou se také zvětšila na 24 položek z 20. Kapacita unifikované mezipaměti L2 byla zvýšena na 1,875 MB a asociativita sady na 10 cest. Sjednocená mezipaměť L3 byla přenesena na balíček místo externího umístění v samostatných čipech. Jeho kapacita byla zvýšena na 36 MB. Stejně jako POWER4 je mezipaměť sdílena dvěma jádry. Ke vyrovnávací paměti se přistupuje prostřednictvím dvou jednosměrných 128bitových sběrnic pracujících na poloviční frekvenci jádra.

Řadič paměti on-die podporuje až 64 GB paměti DDR a DDR2 . Používá vysokofrekvenční sériové sběrnice ke komunikaci s externími vyrovnávacími paměťmi, které propojují duální vložené paměťové moduly (DIMM) s mikroprocesorem.

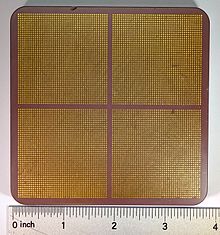

POWER5 obsahuje 276 milionů tranzistorů a má plochu 389 mm 2 . Je vyroben společností IBM v 0,13 μm silikonu na izolátoru (SOI) komplementárním procesu kov – oxid – polovodič (CMOS) s osmi vrstvami propojení mědi . Raznice POWER5 je zabalena buď ve dvoučipovém modulu (DCM), nebo ve vícečipovém modulu (MCM). DCM obsahuje jednu kostku POWER5 a související matici vyrovnávací paměti L3. MCM obsahuje čtyři matrice POWER5 a čtyři vyrovnávací matice L3, jednu pro každou matici POWER5, a měří 95 mm x 95 mm.

Několik procesorů POWER5 ve špičkových systémech lze spojit dohromady a fungovat jako jediný vektorový procesor pomocí technologie zvané ViVA (Virtual Vector Architecture).

POWER5+

POWER5+ je vylepšená iterace modelu POWER5 představeného 4. října 2005. Vylepšení byla zpočátku nižší spotřeba energie, kvůli novějšímu procesu, ve kterém byl vyroben. Čip POWER5+ používá 90nm výrobní proces. To vedlo ke snížení velikosti matrice z 389 mm 2 na 243 mm 2 .

Taktovací frekvence nebyla při startu zvýšena a zůstala mezi 1,5 až 1,9 GHz. Dne 14. února 2006 nové verze zvýšily taktovací frekvenci na 2,2 GHz a poté na 2,3 GHz dne 25. července 2006.

POWER5+ byl zabalen ve stejných balíčcích jako předchozí mikroprocesory POWER5, ale byl také k dispozici v čtyřčipovém modulu (QCM) obsahujícím dvě matrice POWER5+ a dvě vyrovnávací matrice L3, po jedné pro každou matici POWER5+. Tyto čipy QCM běžely na hodinové frekvenci mezi 1,5 a 1,8 GHz.

Uživatelé

IBM používá mikroprocesory DCM a MCM POWER5 v řadách serverů System p a System i , na úložném serveru DS8000 a jako vestavěné mikroprocesory ve svých špičkových tiskárnách Infoprint. Mikroprocesory DCM POWER5 používá IBM ve své špičkové pracovní stanici IntelliStation POWER 285 . Jinými uživateli mikroprocesorů POWER5 jsou Groupe Bull na serverech Escala a Hitachi na počítačích SR11000 s až 128 mikroprocesory POWER5+, které mají několik instalací uvedených v seznamu superpočítačů TOP500 za rok 2007 . IBM používá POWER5+ QCM na serverech System p5 510Q, 520Q, 550Q a 560Q.

Poznámky

Viz také

Reference

- „IBM Preview Power5“. (8. září 2003). Zpráva o mikroprocesoru .

- Clabes, Joachim a kol. (2004). „Návrh a implementace mikroprocesoru POWER5“. Proceedings of 2004 IEEE International Solid-State Circuits Conference .

- Glaskowsky, Peter N. (14. října 2003). „IBM zvyšuje oponu na Power5“. Zpráva o mikroprocesoru .

- Kalla, Ron; Sinharoy, Balaram; Tendler, Joel M. (2004). „Čip IBM Power5: Dvoujádrový vícevláknový procesor“. IEEE Micro .

- Krewell, Kevin (22. prosince 2003). „Power5 vrcholy šířky pásma“. Zpráva o mikroprocesoru .

- Sinharoy, Balaram a kol. (2005). „Mikroarchitektura systému POWER5“. IBM Journal of Research and Development .

- Vance, Ashlee (4. října 2005). „IBM pumpuje unixovou řadu plnou Power5+“ . Registr .

externí odkazy

- Dimenzování Super Heavyweights , srovnání a analýza POWER5 a Montecito, což vysvětluje hlavní změny mezi POWER4 a POWER5 spolu s odhady výkonu

- Vysoce výkonný IBM Power5+ p5-575 Cluster 1600 a DDN S2A9550 Storage , Texas A&M University