Fázově uzamčená smyčka - Phase-locked loop

Fázového závěsu nebo fázový závěs ( PLL ) je řídicí systém , který generuje výstupní signál, jehož fáze se vztahuje k fázi vstupního signálu. Existuje několik různých typů; nejjednodušší je elektronický obvod skládající se z oscilátoru s proměnnou frekvencí a fázového detektoru ve zpětnovazební smyčce . Oscilátor generuje periodický signál a fázový detektor porovnává fázi tohoto signálu s fází vstupního periodického signálu a upravuje oscilátor tak, aby byly fáze shodné.

Udržení vstupní a výstupní fáze v kroku zámku také znamená zachování stejných vstupních a výstupních frekvencí. V důsledku toho může kromě synchronizace signálů smyčka fázového závěsu sledovat vstupní frekvenci nebo může generovat frekvenci, která je násobkem vstupní frekvence. Tyto vlastnosti se používají pro synchronizaci počítačových hodin, demodulaci a frekvenční syntézu .

Fázově uzamčené smyčky jsou široce používány v rádiu , telekomunikacích , počítačích a dalších elektronických aplikacích. Lze je použít k demodulaci signálu, obnovení signálu z hlučného komunikačního kanálu, generování stabilní frekvence na násobcích vstupní frekvence ( syntéza frekvence ) nebo distribuci přesně načasovaných hodinových impulzů v digitálních logických obvodech, jako jsou mikroprocesory . Vzhledem k tomu, že jeden integrovaný obvod může poskytnout kompletní stavební blok s fázově uzamčenou smyčkou, je tato technika široce používána v moderních elektronických zařízeních s výstupními frekvencemi od zlomku hertzů až po mnoho gigahertzů.

Praktické analogie

Analogie automobilových závodů

Jako analogii PLL zvažte závod mezi dvěma vozy. Jeden představuje vstupní frekvenci, druhý frekvenci výstupního napěťově řízeného oscilátoru (VCO) PLL . Každé kolo odpovídá kompletnímu cyklu. Počet kol za hodinu (rychlost) odpovídá frekvenci. Oddělení vozů (vzdálenost) odpovídá fázovému rozdílu mezi dvěma oscilujícími signály.

Po většinu závodu je každý vůz sám a může projet druhým a zajet do druhého. To je analogické PLL v odemčeném stavu.

Pokud však dojde k nehodě, je vztyčena žlutá výstražná vlajka . To znamená, že ani jeden ze závodních vozů nesmí předjíždět a předjíždět druhé auto. Dva závodní vozy představují vstupní a výstupní frekvenci PLL v uzamčeném stavu. Každý jezdec bude měřit fázový rozdíl (zlomek vzdálenosti kolem kola) mezi sebou a druhým závodním vozem. Pokud je zadní řidič příliš daleko, zvýší rychlost, aby mezeru zacelil. Pokud jsou příliš blízko druhého auta, řidič zpomalí. Výsledkem je, že obě závodní auta budou kroužit po trati v uzamčení s pevným fázovým rozdílem (nebo konstantní vzdáleností) mezi nimi. Vzhledem k tomu, že ani jednomu vozu není povoleno zajet druhé, ujedou auta v daném časovém období stejný počet kol. Proto je frekvence obou signálů stejná.

Analogie hodin

Fáze může být úměrná času, takže fázový rozdíl může být časový rozdíl. Hodiny jsou s různou mírou přesnosti fázově uzamčeny (časově uzamčeny) na vedoucí hodiny.

Ponechané samostatně, každé hodiny budou označovat čas mírně odlišnými sazbami. Například nástěnné hodiny mohou být ve srovnání s referenčními hodinami NIST rychlé o několik sekund za hodinu . Časem bude tento časový rozdíl podstatný.

Aby byly nástěnné hodiny synchronizované s referenčními hodinami, majitel každý týden porovnává čas na nástěnných hodinách s přesnějšími hodinami (fázové srovnání) a hodiny resetuje. Pokud se nástěnné hodiny ponechají samy, budou se i nadále lišit od referenčních hodin stejnou rychlostí několika sekund za hodinu.

Některé hodiny mají úpravu časování (rychlé a pomalé ovládání). Když majitel porovnal čas svých nástěnných hodin s referenčním časem, všimli si, že jejich hodiny jsou příliš rychlé. V důsledku toho by majitel mohl časování upravit o malé množství, aby hodiny běžely trochu pomaleji (frekvence). Pokud věci dobře fungují, budou jejich hodiny přesnější než dříve. Při sérii týdenních úprav by představa sekundy nástěnných hodin souhlasila s referenčním časem (uzamčeným jak ve frekvenci, tak ve fázi v rámci stability nástěnných hodin).

Časná elektromechanická verze fázově uzamčené smyčky byla použita v roce 1921 v krátkých synchronizačních hodinách .

Dějiny

Spontánní synchronizaci slabě spojených kyvadlových hodin zaznamenal nizozemský fyzik Christiaan Huygens již v roce 1673. Na přelomu 19. století Lord Rayleigh pozoroval synchronizaci slabě spojených varhanních píšťal a ladiček. V roce 1919 WH Eccles a JH Vincent zjistili, že dva elektronické oscilátory, které byly naladěny tak, aby oscilovaly na mírně odlišných frekvencích, ale které byly spojeny s rezonančním obvodem, budou brzy oscilovat na stejné frekvenci. Automatickou synchronizaci elektronických oscilátorů popsal v roce 1923 Edward Victor Appleton .

V roce 1925 profesor David Robertson, první profesor elektrotechniky na univerzitě v Bristolu , představil ve svém designu hodin fázové zamykání, aby ovládal údery zvonu Great George v nové Wills Memorial Building. Robertsonovy hodiny obsahovaly elektromechanické zařízení, které dokázalo měnit rychlost oscilace kyvadla, a odvozovaly korekční signály z obvodu, který každé ráno v 10.00 GMT porovnával fázi kyvadla s příchozím telegrafním pulsem z Greenwichské observatoře. Kromě zahrnutí ekvivalentů každého prvku moderní elektronické PLL byl Robertsonův systém pozoruhodný tím, že jeho fázový detektor byl reléovou logickou implementací fázového/frekvenčního detektoru, který nebyl v elektronických obvodech viděn až do 70. let minulého století. Robertson práce předcházel výzkum k tomu, co bylo později jmenoval phase-lock loop v roce 1932, když britští vědci vyvinuli alternativu k Edwin Armstrong je superhet , na homodynní nebo přímé přeměny přijímače . V homodynovém nebo synchrodynovém systému byl místní oscilátor naladěn na požadovanou vstupní frekvenci a vynásoben vstupním signálem. Výsledný výstupní signál obsahoval původní informace o modulaci. Záměrem bylo vyvinout alternativní přijímací obvod, který by vyžadoval méně laděných obvodů než superheterodynový přijímač. Protože lokální oscilátor by se rychle ubíral na frekvenci, byl na oscilátor aplikován signál automatické korekce, který jej udržuje ve stejné fázi a frekvenci požadovaného signálu. Tato technika byla popsána v roce 1932 v článku Henri de Bellescize ve francouzském časopise L'Onde Électrique .

V analogových televizních přijímačích, přinejmenším od konce třicátých let, jsou horizontální a vertikální zametací obvody fázově uzamčené smyčky blokovány synchronizačními impulsy v přenosovém signálu.

Když společnost Signetics v roce 1969 představila řadu monolitických integrovaných obvodů, jako je NE565, což byly kompletní smyčkové systémy s fázovým zámkem na čipu, aplikace pro tuto techniku se znásobila. O několik let později představila RCA „ CD4046 “ CMOS Micropower Phase-Locked Loop, která se stala populárním integrovaným obvodem.

Struktura a funkce

Mechanismy smyčky fázového závěsu mohou být implementovány buď jako analogové nebo digitální obvody. Obě implementace používají stejnou základní strukturu. Analogové obvody PLL zahrnují čtyři základní prvky:

- Fázový detektor ,

- Dolní propust ,

- Napětí řízený oscilátor a

- cesta zpětné vazby (která může zahrnovat dělič frekvence ).

Variace

Existuje několik variací PLL. Některé termíny, které se používají, jsou analogová smyčka fázového závěsu (APLL), označovaná také jako lineární smyčka fázového závěsu (LPLL), smyčka digitálního fázového závěsu (DPLL), všechna smyčka digitálního fázového závěsu (ADPLL) a softwarová fáze -zablokovaná smyčka (SPLL).

- Analogový nebo lineární PLL (APLL)

- Fázový detektor je analogový multiplikátor. Smyčkový filtr je aktivní nebo pasivní. Používá napěťově řízený oscilátor (VCO). APLL se říká, že je typu II, pokud jeho smyčkový filtr má přenosovou funkci s přesně jedním pólem na počátku (viz také Eganova domněnka o rozsahu vtažení APLL typu II ).

- Digitální PLL (DPLL)

- Analogový PLL s digitálním fázovým detektorem (jako XOR, edge-trigger JK, fázový frekvenční detektor). Může mít ve smyčce digitální dělič.

- Všechny digitální PLL (ADPLL)

- Fázový detektor, filtr a oscilátor jsou digitální. Používá numericky řízený oscilátor (NCO).

- Software PLL (SPLL)

- Funkční bloky jsou implementovány spíše softwarem než specializovaným hardwarem.

- Nabíjecí čerpadlo PLL (CP-PLL)

- CP-PLL je modifikací fázově uzamčených smyček s detektorem fázové frekvence a signály čtvercového průběhu. Viz také Gardnerovy dohady o CP-PLL .

Parametry výkonu

- Typ a objednávka.

- Frekvenční rozsahy : rozsah přidržení (rozsah sledování), rozsah zatažení (rozsah zachycení, rozsah akvizice), rozsah zablokování. Viz také Gardnerův problém ohledně rozsahu zablokování , Eganova domněnka ohledně rozsahu zatažení typu II APLL .

- Šířka pásma smyčky: Definování rychlosti řídicí smyčky.

- Přechodná odezva: Stejně jako překročení a doba ustálení s určitou přesností (například 50 ppm).

- Chyby v ustáleném stavu: Jako chyba zbývající fáze nebo časování.

- Čistota výstupního spektra: Jako postranní pásma generovaná určitým zvlněním ladicího napětí VCO.

- Fázový šum: Definováno šumovou energií v určitém frekvenčním pásmu (například 10 kHz offset od nosné). Velmi závisí na fázovém šumu VCO, šířce pásma PLL atd.

- Obecné parametry: Jako je spotřeba energie, rozsah napájecího napětí, výstupní amplituda atd.

Aplikace

Fázově uzamčené smyčky jsou široce používány pro účely synchronizace ; ve vesmírné komunikaci pro koherentní demodulaci a rozšíření prahů , bitovou synchronizaci a synchronizaci symbolů. Fázově uzamčené smyčky lze také použít k demodulaci frekvenčně modulovaných signálů. V rádiových vysílačích se PLL používá k syntéze nových frekvencí, které jsou násobkem referenční frekvence, se stejnou stabilitou jako referenční frekvence.

Mezi další aplikace patří

- Demodulace z frekvenční modulace (FM): Je-li PLL je uzamčen na FM signálu, VCO sleduje okamžité frekvence vstupního signálu. Filtrované chybové napětí, které ovládá VCO a udržuje zámek se vstupním signálem, je demodulován výstup FM. Přenosové charakteristiky VCO určují linearitu demodulovaného výstupu. Vzhledem k tomu, že VCO použité v PLL s integrovaným obvodem je vysoce lineární, je možné realizovat vysoce lineární demodulátory FM.

- Demodulace klíčování s frekvenčním posunem (FSK): V digitální datové komunikaci a počítačových periferiích jsou binární data přenášena pomocí nosné frekvence, která je posunuta mezi dvěma přednastavenými frekvencemi.

- Obnova malých signálů, které by jinak byly ztraceny v šumu ( blokovací zesilovač pro sledování referenční frekvence)

- Obnovení informací o časování hodin z datového proudu, například z diskové jednotky

- Taktovací multiplikátory v mikroprocesorech, které umožňují interním procesorovým prvkům běžet rychleji než externí připojení, při zachování přesných časovacích vztahů

- Demodulace modemů a dalších tónových signálů pro telekomunikace a dálkové ovládání .

- DSP z obrazových signálů; Smyčky fázového závěsu se také používají k synchronizaci fáze a frekvence se vstupním analogovým video signálem, takže jej lze vzorkovat a digitálně zpracovávat

- Mikroskopie atomové síly v režimu modulace frekvence , k detekci změn rezonanční frekvence konzoly v důsledku interakcí hrot -povrch

- DC motorový pohon

Obnovení hodin

Některé datové toky, zejména vysokorychlostní sériové datové toky (například surový datový tok z magnetické hlavy diskové jednotky), jsou odesílány bez doprovodných hodin. Přijímač generuje hodiny z přibližné referenční frekvence a poté fázově zarovnává přechody v datovém proudu pomocí PLL. Tento proces se označuje jako obnova hodin . Aby toto schéma fungovalo, musí mít datový tok dostatečně častý přechod, aby opravil jakýkoli posun v oscilátoru PLL. Typicky se nějaký druh řádkového kódu , jako je kódování 8b/10b , používá k nastavení pevné horní hranice maximální doby mezi přechody.

Zkosení

Pokud jsou hodiny odesílány souběžně s daty, lze je použít k vzorkování dat. Protože hodiny musí být přijaty a zesíleny, než mohou pohánět klopné obvody, které vzorkují data, bude mezi detekovanou hranou hodin a oknem přijatých dat konečné a procesně, teplotně a napěťově závislé zpoždění. Toto zpoždění omezuje frekvenci odesílání dat. Jedním ze způsobů, jak eliminovat toto zpoždění, je zahrnout redukci PLL na přijímací straně, takže hodiny na každém datovém klopném obvodu jsou fázově přizpůsobeny přijímaným hodinám. V tomto typu aplikace se často používá speciální forma PLL nazývaná smyčka se zpožděním (DLL).

Generování hodin

Mnoho elektronických systémů obsahuje procesory různých druhů, které pracují na stovkách megahertzů. Hodiny dodávané do těchto procesorů obvykle pocházejí z generátorů hodin generátoru PLL, které násobí referenční hodiny s nižší frekvencí (obvykle 50 nebo 100 MHz) až do provozní frekvence procesoru. Multiplikační faktor může být poměrně velký v případech, kdy je pracovní frekvence několik gigahertzů a referenční krystal je jen desítky nebo stovky megahertzů.

Rozprostřené spektrum

Všechny elektronické systémy vyzařují nežádoucí radiofrekvenční energii. Různé regulační agentury (například FCC ve Spojených státech) stanovují limity vyzařované energie a veškerých interferencí, které způsobují. Vyzařovaný šum se obecně objevuje na ostrých spektrálních špičkách (obvykle na provozní frekvenci zařízení a několika harmonických). Návrhář systému může použít PLL s rozprostřeným spektrem ke snížení interference s přijímači s vysokým Q rozložením energie na větší část spektra. Například změnou pracovní frekvence nahoru a dolů o malé množství (asi 1%) může zařízení běžící na stovkách megahertzů rozložit své rušení rovnoměrně na několik megahertzů spektra, což drasticky snižuje množství šumu viditelného ve vysílání Rádiové kanály FM , které mají šířku pásma několik desítek kilohertz.

Distribuce hodin

Referenční hodiny obvykle vstupují do čipu a pohání smyčku fázového závěsu ( PLL ), která pak řídí distribuci hodin systému. Rozložení hodin je obvykle vyvážené, aby hodiny dorazily na každý koncový bod současně. Jedním z těchto koncových bodů je vstup zpětné vazby PLL. Funkcí PLL je porovnat distribuované hodiny s příchozími referenčními hodinami a měnit fázi a frekvenci jejího výstupu, dokud nejsou referenční a zpětnovazební hodiny shodné s fází a frekvencí.

PLL jsou všudypřítomné - ladí hodiny v systémech o několik stop napříč, stejně jako hodiny v malých částech jednotlivých čipů. Někdy nemusí být referenční hodiny ve skutečnosti čistými hodinami, ale spíše datovým tokem s dostatečným počtem přechodů, aby PLL dokázala z tohoto proudu obnovit běžné hodiny. Někdy mají referenční hodiny stejnou frekvenci jako hodiny poháněné distribucí hodin, jindy mohou být distribuované hodiny racionálním násobkem reference.

Detekce AM

PLL lze použít k synchronní demodulaci amplitudově modulovaných (AM) signálů. PLL obnovuje fázi a frekvenci nosiče příchozího signálu AM. Rekuperovaná fáze na VCO se liší od nosné o 90 °, takže je posunuta ve fázi tak, aby odpovídala, a poté se přivádí do multiplikátoru. Výstup multiplikátoru obsahuje součtové i rozdílové kmitočtové signály a demodulovaný výstup je získán nízkoprůchodovým filtrováním. Protože PLL reaguje pouze na nosné frekvence, které jsou velmi blízké výstupu VCO, detektor PLL AM vykazuje vysoký stupeň selektivity a odolnosti proti rušení, což u běžných AM demodulátorů špičkového typu není možné. Smyčka však může ztratit zámek tam, kde signály AM mají hloubku modulace 100%.

Chvění a redukce šumu

Jednou žádoucí vlastností všech PLL je, že referenční a zpětnovazební hodinové hrany jsou uvedeny do velmi těsného vyrovnání. Průměrný časový rozdíl mezi fázemi těchto dvou signálů, když PLL dosáhne zámku, se nazývá statický fázový posun (také se nazývá fázová chyba v ustáleném stavu ). Rozptyl mezi těmito fázemi se nazývá sledování jitteru . V ideálním případě by měl být statický fázový posun nulový a kolísání sledování by mělo být co nejnižší.

Fázový šum je dalším typem jitteru pozorovaného v PLL a je způsoben samotným oscilátorem a prvky používanými v obvodu řízení frekvence oscilátoru. O některých technologiích je známo, že v tomto ohledu fungují lépe než jiné. Nejlepší digitální PLL jsou konstruovány s logickými prvky spojenými s emitorem ( ECL ) na úkor vysoké spotřeby energie. Aby byl v obvodech PLL nízký fázový šum, je nejlepší se vyhnout saturačním logickým rodinám, jako je logika tranzistor-tranzistor ( TTL ) nebo CMOS .

Další žádoucí vlastností všech PLL je, že fáze a frekvence generovaných hodin nejsou ovlivněny rychlými změnami napětí napájecího a pozemního napájecího vedení, stejně jako napětí substrátu, na kterém jsou obvody PLL vyrobeny. Toto se nazývá potlačení hluku substrátu a napájení . Čím vyšší je potlačení hluku, tím lépe.

K dalšímu zlepšení fázového šumu výstupu lze použít vstřikovací zamknutý oscilátor sledující VCO v PLL.

Frekvenční syntéza

V digitálních bezdrátových komunikačních systémech (GSM, CDMA atd.) Se PLL používají k zajištění převodu místního oscilátoru během přenosu a převodu dolů během příjmu. Ve většině mobilních telefonů byla tato funkce z velké části integrována do jediného integrovaného obvodu, aby se snížily náklady a velikost sluchátka. Kvůli vysokému výkonu požadovanému od terminálů základnových stanic jsou však vysílací a přijímací obvody konstruovány s diskrétními součástmi, aby se dosáhlo požadovaných úrovní výkonu. Moduly lokálního oscilátoru GSM jsou typicky postaveny s integrovaným obvodem frekvenčního syntetizátoru a diskrétními rezonátorovými VCO.

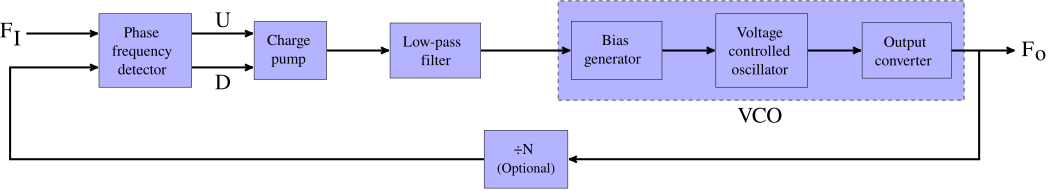

Blokové schéma

Fázový detektor porovnává dva vstupní signály a vytváří chybový signál, který je úměrný jejich fázovému rozdílu. Chybový signál je poté filtrován dolním průchodem a použit k pohonu VCO, který vytváří výstupní fázi. Výstup je veden volitelným děličem zpět na vstup systému, čímž vzniká negativní zpětná vazba . Pokud se výstupní fáze unáší, chybový signál se zvýší, přičemž fáze VCO bude v opačném směru, aby se snížila chyba. Proto je výstupní fáze uzamčena k fázi na druhém vstupu. Tento vstup se nazývá reference.

Analogové fázově uzamčené smyčky jsou obecně konstruovány s analogovým fázovým detektorem, nízkoprůchodovým filtrem a VCO umístěnými v konfiguraci negativní zpětné vazby . Digitální smyčka s fázovým zámkem používá digitální fázový detektor; může mít také dělič ve zpětnovazební cestě nebo v referenční cestě, nebo obojí, aby se frekvence výstupního signálu PLL stala racionálním násobkem referenční frekvence. Neceločíselný násobek referenční frekvence může být také vytvořen nahrazením jednoduchého čítače dělení číslem N ve zpětnovazební cestě programovatelným čítačem polykání pulsů . Tato technika se obvykle označuje jako frakční-N syntetizátor nebo frakční-N PLL.

Oscilátor generuje periodický výstupní signál. Předpokládejme, že zpočátku má oscilátor téměř stejnou frekvenci jako referenční signál. Pokud fáze z oscilátoru klesne za referenční, fázový detektor změní řídicí napětí oscilátoru tak, aby se zrychlil. Podobně, pokud se fáze plíží před referencí, fázový detektor změní řídicí napětí, aby zpomalil oscilátor. Protože zpočátku může být oscilátor daleko od referenční frekvence, praktické fázové detektory mohou také reagovat na frekvenční rozdíly, aby se zvýšil rozsah blokování přípustných vstupů. V závislosti na aplikaci poskytuje užitečný výstup systému PLL buď výstup řízeného oscilátoru, nebo řídicí signál do oscilátoru.

Elementy

Fázový detektor

Fázový detektor (PD) generuje napětí, které představuje fázový rozdíl mezi dvěma signály. V PLL jsou dva vstupy fázového detektoru referenční vstup a zpětná vazba od VCO. Výstupní napětí PD se používá k řízení VCO tak, že fázový rozdíl mezi dvěma vstupy je udržován konstantní, což z něj činí systém negativní zpětné vazby.

Různé typy fázových detektorů mají různé výkonové charakteristiky.

Například frekvence směšovač generuje harmonické, který přidává složitost v aplikacích, kde spektrální čistoty signálu VCO je důležité. Výsledná nechtěná (podvržená) postranní pásma, nazývaná také „ referenční ostruhy “, mohou dominovat požadavkům filtru a snížit rozsah zachycení hluboko pod nebo prodloužit dobu blokování nad rámec požadavků. V těchto aplikacích se používají složitější digitální fázové detektory, které na svém výstupu nemají tak závažnou referenční ostruhovou složku. Také když je v zámku, fázový rozdíl v ustáleném stavu na vstupech pomocí tohoto typu fázového detektoru je téměř 90 stupňů.

V aplikacích PLL je často nutné vědět, kdy je smyčka mimo zámek. Složitější digitální fázově-frekvenční detektory mají obvykle výstup, který umožňuje spolehlivou indikaci stavu mimo zámek.

Brána XOR se často používá pro digitální PLL jako účinný, ale jednoduchý fázový detektor. Může být také použit v analogovém smyslu s pouze malou změnou obvodů.

Filtr

Blok běžně nazývaný smyčkový filtr PLL (obvykle dolní propust) má obecně dvě odlišné funkce.

Primární funkcí je určit dynamiku smyčky, nazývanou také stabilita . Takto smyčka reaguje na poruchy, jako jsou změny referenční frekvence, změny děliče zpětné vazby nebo při spuštění. Běžné úvahy jsou rozsah, ve kterém může smyčka dosáhnout zámku (rozsah zasunutí, rozsah zámku nebo rozsah zachycení), jak rychle smyčka dosáhne zámku (doba zámku, doba zablokování nebo doba usazení ) a chování tlumení . V závislosti na aplikaci to může vyžadovat jeden nebo více z následujících: jednoduchý poměr (zesílení nebo útlum), integrální (dolní propust) a/nebo derivát ( horní propust ). Parametry smyčky, které se běžně zkoumají, jsou zisk a smyčka fáze . K návrhu této funkce se používají běžné koncepce v teorii řízení včetně PID regulátoru .

Druhým společným hlediskem je omezení množství energie referenčního kmitočtu (zvlnění) objevujícího se na výstupu fázového detektoru, které je poté aplikováno na řídicí vstup VCO. Tato frekvence moduluje VCO a vytváří postranní pásma FM běžně nazývaná „referenční ostruhy“.

Návrhu tohoto bloku může dominovat některá z těchto úvah, nebo se může jednat o složitý proces, který spojuje interakce těchto dvou. Typickými kompromisy jsou zvyšování šířky pásma, obvykle zhoršuje stabilitu, nebo příliš silné tlumení pro lepší stabilitu sníží rychlost a prodlouží dobu usazování. Často je také ovlivněn fázový šum.

Oscilátor

Všechny smyčky fázového závěsu používají oscilátorový prvek s možností proměnné frekvence. To může být analogový VCO buď poháněný analogovými obvody v případě APLL, nebo řízený digitálně pomocí převodníku digitálního signálu na analogový, jak je tomu u některých návrhů DPLL. V ADPLL se používají čisté digitální oscilátory, jako je numericky řízený oscilátor.

Zpětná vazba a volitelný dělič

PLL mohou obsahovat dělič mezi oscilátorem a zpětnovazebním vstupem do fázového detektoru pro výrobu frekvenčního syntetizátoru . Programovatelný dělič je zvláště užitečný v aplikacích rádiových vysílačů, protože z jednoho stabilního, přesného, ale drahého referenčního oscilátoru řízeného křemennými krystaly lze vyrobit velké množství přenosových frekvencí .

Některé PLL také obsahují dělič mezi referenčními hodinami a referenčním vstupem do fázového detektoru. Pokud dělič ve zpětnovazební cestě dělí a dělí referenční vstupní dělič , umožňuje PLL znásobit referenční frekvenci o . Může se zdát jednodušší podávat PLL nižší frekvencí, ale v některých případech může být referenční frekvence omezena jinými problémy a pak je referenční dělič užitečný.

Násobení kmitočtu lze také dosáhnout uzamčením výstupu VCO na N -té harmonické referenčního signálu. Namísto jednoduchého fázového detektoru využívá konstrukce harmonický mixér (vzorkovací mixér). Harmonický mixér mění referenční signál na impulsní řadu bohatou na harmonické. Výstup VCO je hrubě naladěn tak, aby se blížil jedné z těchto harmonických. V důsledku toho požadovaný výstup směšovače harmonické (představující rozdíl mezi N harmonickou a VCO výstupem) spadá do propustného pásma smyčkového filtru.

Je třeba také poznamenat, že zpětná vazba není omezena na dělič frekvence. Tímto prvkem mohou být další prvky, například multiplikátor frekvence nebo směšovač. Z multiplikátoru bude výstup VCO sub-násobkem (spíše než násobkem) referenční frekvence. Mixér může překládat frekvenci VCO pomocí pevného offsetu. Může to být také jejich kombinace. Příkladem je dělič za mixérem; to umožňuje děličku pracovat na mnohem nižší frekvenci než VCO bez ztráty zesílení smyčky.

Modelování

Model časové domény APLL

Rovnice řídící smyčku fázového závěsu s analogovým multiplikátorem jako fázovým detektorem a lineárním filtrem lze odvodit následujícím způsobem. Nechejte vstup do fázového detektoru a výstup VCO je s fázemi a . Funkce a popis průběhů signálů. Poté je výstup fázového detektoru dán pomocí

Frekvence VCO je obvykle brána jako funkce vstupu VCO jako

kde je citlivost VCO a je vyjádřena v Hz / V; je volně běžící frekvence VCO.

Smyčkový filtr lze popsat soustavou lineárních diferenciálních rovnic

kde je vstup filtru, je výstupem filtru, je -by- matice, . představuje počáteční stav filtru. Symbol hvězdy je konjugovaná transpozice .

Následující systém tedy popisuje PLL

kde je počáteční fázový posun.

Fázový doménový model APLL

Zvažte vstup PLL a VCO výstup jsou vysokofrekvenční signály. Pak pro všechny po částech diferencovatelné -periodické funkce a existuje funkce taková, že výstup filtru

ve fázové doméně je asymptoticky stejná (rozdíl je malý vzhledem k frekvencím) k výstupu filtru v časové doméně. Zde funkce je charakteristický fázového detektoru .

Označte fázovým rozdílem

Následující dynamický systém pak popisuje chování PLL

Zde ; je frekvence referenčního oscilátoru (předpokládáme, že je konstantní).

Příklad

Zvažte sinusové signály

a jednoduchý jednopólový RC obvod jako filtr. Model časové domény má formu

Charakteristiky PD pro tyto signály se rovnají

Fázový doménový model má tedy formu

Tento systém rovnic je ekvivalentní rovnici matematického kyvadla

Linearizovaný model fázové domény

Smyčky fázového závěsu lze také analyzovat jako řídicí systémy pomocí Laplaceovy transformace . Odpověď smyčky lze zapsat jako

Kde

- je výstupní fáze v radiánech

- je vstupní fáze v radiánech

- je zisk fázového detektoru ve voltech na radián

- je zisk VCO v radiánech za sekundu

- je funkce přenosu smyčkového filtru (bezrozměrná)

Vlastnosti smyčky lze ovládat vložením různých typů smyčkových filtrů. Nejjednodušší filtr je jednopólový RC obvod . Funkce přenosu smyčky v tomto případě je

Odpověď smyčky se stává:

Toto je forma klasického harmonického oscilátoru . Jmenovatel může souviset se systémem druhého řádu:

kde je faktor tlumení a je vlastní frekvence smyčky.

U jednopólového RC filtru

Vlastní frekvence smyčky je měřítkem doby odezvy smyčky a faktor tlumení je míra překročení a vyzvánění. V ideálním případě by přirozená frekvence měla být vysoká a faktor tlumení by měl být blízko 0,707 (kritické tlumení). S jednopólovým filtrem není možné nezávisle ovládat frekvenci smyčky a faktor tlumení. V případě kritického tlumení

Mírně účinnější filtr, zpožděný olověný filtr obsahuje jeden pól a jednu nulu. Toho lze dosáhnout dvěma odpory a jedním kondenzátorem. Funkce přenosu pro tento filtr je

Tento filtr má dvě časové konstanty

Nahrazením výše získáme následující přirozenou frekvenci a faktor tlumení

Komponenty smyčkového filtru lze vypočítat nezávisle pro danou vlastní frekvenci a faktor tlumení

Reálný návrh smyčkového filtru může být mnohem složitější, např. Pomocí filtrů vyššího řádu ke snížení různých typů nebo zdroje fázového šumu. (Viz odkaz D Banerjee níže)

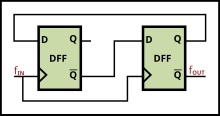

Implementace digitální fázově uzamčené smyčky v softwaru

Digitální fázově uzamčené smyčky lze implementovat v hardwaru pomocí integrovaných obvodů, jako je CMOS 4046. S tím, jak se mikrokontroléry zrychlují, však může mít smysl implementovat smyčku fázového závěsu do softwaru pro aplikace, které nevyžadují uzamčení signálů v MHz rozsah nebo rychlejší, například přesné ovládání otáček motoru. Softwarová implementace má několik výhod, včetně snadného přizpůsobení zpětnovazební smyčky, včetně změny poměru násobení nebo dělení mezi sledovaným signálem a výstupním oscilátorem. Softwarová implementace je navíc užitečná pro pochopení a experimentování. Jako příklad smyčky fázového závěsu implementované pomocí detektoru fázové frekvence je uveden v MATLABu, protože tento typ fázového detektoru je robustní a snadno implementovatelný.

% This example is written in MATLAB

% Initialize variables

vcofreq = zeros(1, numiterations);

ervec = zeros(1, numiterations);

% Keep track of last states of reference, signal, and error signal

qsig = 0; qref = 0; lref = 0; lsig = 0; lersig = 0;

phs = 0;

freq = 0;

% Loop filter constants (proportional and derivative)

% Currently powers of two to facilitate multiplication by shifts

prop = 1 / 128;

deriv = 64;

for it = 1:numiterations

% Simulate a local oscillator using a 16-bit counter

phs = mod(phs + floor(freq / 2 ^ 16), 2 ^ 16);

ref = phs < 32768;

% Get the next digital value (0 or 1) of the signal to track

sig = tracksig(it);

% Implement the phase-frequency detector

rst = ~ (qsig & qref); % Reset the "flip-flop" of the phase-frequency

% detector when both signal and reference are high

qsig = (qsig | (sig & ~ lsig)) & rst; % Trigger signal flip-flop and leading edge of signal

qref = (qref | (ref & ~ lref)) & rst; % Trigger reference flip-flop on leading edge of reference

lref = ref; lsig = sig; % Store these values for next iteration (for edge detection)

ersig = qref - qsig; % Compute the error signal (whether frequency should increase or decrease)

% Error signal is given by one or the other flip flop signal

% Implement a pole-zero filter by proportional and derivative input to frequency

filtered_ersig = ersig + (ersig - lersig) * deriv;

% Keep error signal for proportional output

lersig = ersig;

% Integrate VCO frequency using the error signal

freq = freq - 2 ^ 16 * filtered_ersig * prop;

% Frequency is tracked as a fixed-point binary fraction

% Store the current VCO frequency

vcofreq(1, it) = freq / 2 ^ 16;

% Store the error signal to show whether signal or reference is higher frequency

ervec(1, it) = ersig;

end

V tomto příkladu se předpokládá , že sledovací pole obsahuje referenční signál, který má být sledován. Oscilátor je implementován čítačem, přičemž nejvýznamnější bit čítače indikuje stav zapnutí/vypnutí oscilátoru. Tento kód simuluje dva klopné obvody typu D, které obsahují komparátor fázové frekvence. Pokud má referenční nebo signál kladnou hranu, odpovídající klopný obvod se přepne vysoko. Jakmile je referenční i signál vysoký, oba klopné obvody se resetují. Který klopný obvod je vysoký, v tu chvíli určuje, zda reference nebo signál vede toho druhého. Chybový signál je rozdíl mezi těmito dvěma klopnými hodnotami. Filtr nula pólů je implementován přidáním chybového signálu a jeho derivace do filtrovaného chybového signálu. To je zase integrováno k nalezení frekvence oscilátoru.

V praxi by člověk pravděpodobně do zpětné vazby této smyčky fázového závěsu vložil další operace. Pokud by například smyčka fázového závěsu implementovala multiplikátor frekvence, signál oscilátoru by mohl být rozdělen na frekvenci, než bude porovnán s referenčním signálem.

Viz také

- Frekvenčně uzamčená smyčka

- Fázově uzavřená smyčka nabíjecího čerpadla

- Obnova nosiče

- Kruhová mapa -jednoduchý matematický model fázově uzamčené smyčky ukazující zamykání režimu i chaotické chování.

- Smyčka Costas

- Zpožděná smyčka (DLL)

- Přijímač přímé konverze

- Přímý digitální syntezátor

- Kalmanův filtr

- PLL multibit

- Shortt-Synchronome clock -Slave kyvadlo fázově uzamčeno na master (asi 1921)

Poznámky

Reference

Další čtení

- Banerjee, Dean (2006), PLL Performance, Simulation and Design Handbook (4th ed.), National Semiconductor , archivováno z originálu dne 2012-09-02 , vyvoláno 2012-12-04.

- Best, RE (2003), Phase-closed Loops: Design, Simulation and Applications , McGraw-Hill, ISBN 0-07-141201-8

- de Bellescize, Henri (červen 1932), „La réception Synchrone“, L'Onde Electrique , 11 : 230–240

- Dorf, Richard C. (1993), The Electrical Engineering Handbook , Boca Raton: CRC Press, Bibcode : 1993eeh..book ..... D , ISBN 0-8493-0185-8

- Egan, William F. (1998), Phase-Lock Basics , John Wiley & Sons. (poskytuje užitečné skripty Matlab pro simulaci)

- Egan, William F. (2000), Frequency Synthesis by Phase Lock (2. vyd.), John Wiley and Sons. (poskytuje užitečné skripty Matlab pro simulaci)

- Gardner, Floyd M. (2005), Phaselock Techniques (3. vyd.), Wiley-Interscience, ISBN 978-0-471-43063-6

- Klapper, J .; Frankle, JT (1972), Phase-Locked and Frequency-Feedback Systems , Academic Press. (FM demodulace)

- Kundert, Ken (srpen 2006), Predicting the Phase Noise and Jitter of PLL-Based Frequency Synthesizers (PDF) (4g ed.), Designerer's Guide Consulting, Inc.

- Liu, Mingliang (21. února 2006), Build a 1,5 V 2,4 GHz CMOS PLL , Wireless Net Design Line, archivováno z originálu 1. července 2010. Článek o návrhu standardního PLL IC pro aplikace Bluetooth.

- Wolaver, Dan H. (1991), Phase-Locked Loop Circuit Design , Prentice Hall, ISBN 0-13-662743-9

externí odkazy

- Fázově uzamčený smyčkový primer - obsahuje vložené video

- Excel Unusual hostuje animovaný model PLL a výukové programy pro kódování takového modelu .

![{\ displaystyle {\ begin {aligned} {\ dot {x}} & =-{\ frac {1} {RC}} x+{\ frac {1} {RC}} A_ {1} A_ {2} \ sin (\ theta _ {1} (t)) \ cos (\ theta _ {2} (t)), \\ [6pt] {\ dot {\ theta}} _ {2} & = \ omega _ {\ text {free}}+g_ {v} (c^{*} x) \ end {aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/7aa30f8d69878ef11010da5b8a238c9811b425c7)

![{\ begin {aligned} {\ dot x} & =-{\ frac {1} {RC}} x+{\ frac {1} {RC}} {\ frac {A_ {1} A_ {2}} {2 }} \ sin (\ theta _ {{\ \ Delta}}), \\ [6pt] {\ dot \ theta} _ {{\ Delta}} & = \ omega _ {{\ \ Delta}}-g_ {v} (c^{{*}} x). \ end {aligned}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a27dc4e09c9f27ca06eda5c20cfd62db61852aa9)

![{\ begin {aligned} x & = {\ frac {{\ dot \ theta} _ {2}-\ omega _ {2}} {g_ {v} c^{*}}} = {\ frac {\ omega _ {1}-{\ dot \ theta} _ {{\ Delta}}-\ omega _ {2}} {g_ {v} c^{*}}}, \\ [6pt] {\ dot x} & = {\ frac {{\ ddot \ theta} _ {2}} {g_ {v} c^{*}}}, \\ [6pt] \ theta _ {1} & = \ omega _ {1} t+\ Psi , \\ [6pt] \ theta _ {{\ Delta}} & = \ theta _ {1}-\ theta _ {2}, \\ [6pt] {\ dot \ theta} _ {{\ Delta}} & = {\ dot \ theta} _ {1}-{\ dot \ theta} _ {2} = \ omega _ {1}-{\ dot \ theta} _ {2}, \\ [6pt] & {\ frac {1} {g_ {v} c^{*}}} {\ ddot \ theta} _ {{\ Delta}}-{\ frac {1} {g_ {v} c^{*} RC}} {\ tečka \ theta} _ {{\ Delta}}-{\ frac {A_ {1} A_ {2}} {2RC}} \ sin \ theta _ {{\ Delta}} = {\ frac {\ omega _ {2 }-\ omega _ {1}} {g_ {v} c^{*} RC}}. \ end {aligned}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e270e7df2f932355fbcf2a304ac607c0247b75f7)