Fyzický design (elektronika) - Physical design (electronics)

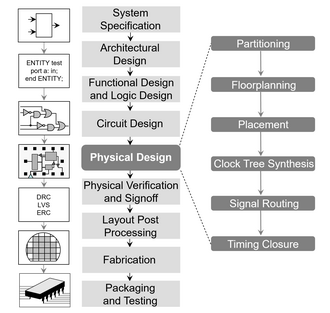

V návrhu integrovaných obvodů je fyzický návrh krokem ve standardním návrhovém cyklu, který následuje po návrhu obvodu . V tomto kroku se znázornění obvodů komponentů (zařízení a propojení) designu převedou na geometrická zobrazení tvarů, která při výrobě v odpovídajících vrstvách materiálů zajistí požadované fungování komponent. Tato geometrická reprezentace se nazývá uspořádání integrovaných obvodů . Tento krok je obvykle rozdělen do několika dílčích kroků, které zahrnují jak návrh, tak ověření a ověření rozložení.

Moderní design integrovaných obvodů (IC) se dělí na front-end design pomocí HDL a back-end design nebo fyzický design . Vstupy do fyzického návrhu jsou (i) netlist, (ii) informace o knihovně na základních zařízeních v návrhu a (iii) technologický soubor obsahující výrobní omezení. Fyzický design je obvykle zakončen Layout Post Processing , ve kterém jsou prováděny úpravy a doplňky rozložení čipu. Poté následuje proces výroby nebo výroby, kde se návrhy přenášejí na silikonové matrice, které se pak balí do integrovaných obvodů.

Každá z výše uvedených fází má s nimi spojené návrhové toky. Tyto návrhové toky stanoví proces a vodicí linie / rámec pro danou fázi. Tok fyzického návrhu využívá technologické knihovny poskytované výrobními domy. Tyto soubory technologií poskytují informace týkající se typu použitého křemíkového plátku, použitých standardních článků, pravidel rozložení (jako DRC ve VLSI) atd.

Divize

Fyzický design IC se obvykle dělí na plně vlastní a částečně vlastní design.

- Full-Custom: Designer má plnou flexibilitu při návrhu rozložení, nepoužívají se žádné předdefinované buňky.

- Semi-Custom: Používají se předem navržené buňky knihovny (nejlépe testované pomocí DFM ), designer má flexibilitu v umístění buněk a směrování.

Jeden může použít ASIC pro Full Custom design a FPGA pro Semi-Custom design flow. Důvodem je, že jeden má flexibilitu navrhovat / upravovat návrhové bloky od knihoven poskytovaných dodavatelem v ASIC. Tato flexibilita chybí pro polo-vlastní toky využívající FPGA (např. Altera ).

Tok fyzického designu ASIC

Hlavní kroky v toku fyzického návrhu ASIC jsou:

- Návrh Netlist (po syntéze)

- Půdorys

- Rozdělení na oddíly

- Umístění

- Syntéza hodinového stromu (CTS)

- Směrování

- Fyzické ověření

- Zpracování rozvržení s generováním maskových dat

Tyto kroky jsou pouze základy. Existují podrobné toky PD, které se používají v závislosti na použitých nástrojích a metodice / technologii. Některé nástroje / software použité v back-end designu jsou:

- Cadence (Cadence Encounter RTL Compiler, Encounter Digital Implementation, Cadence Voltus IC Power Integrity Solution, Cadence Tempus Timing Signoff Solution)

- Synopsys (Design Compiler, IC Compiler II, IC Validator, PrimeTime, PrimePower, PrimeRail)

- Magma (BlastFusion atd.)

- Mentor Graphics (Olympus SoC, IC-Station, Caliber)

Tok fyzického návrhu ASIC využívá technologické knihovny poskytované výrobními domy. Technologie jsou běžně klasifikovány podle minimální velikosti funkce. Standardní velikosti v pořadí miniaturizace jsou 2 μm , 1 μm , 0,5 μm, 0,35 μm, 0,25 μm, 180 nm , 130 nm, 90 nm, 65 nm, 45 nm, 28 nm, 22 nm, 18 nm, 14 nm atd. Mohou být také klasifikovány podle hlavních výrobních přístupů: n-Well process, twin-well process, SOI process, etc.

Navrhněte netlist

Fyzický design je založen na netlistu, který je konečným výsledkem procesu syntézy. Syntéza převádí návrh RTL obvykle kódovaný ve VHDL nebo Verilog HDL na popisy na úrovni brány, které další sada nástrojů dokáže číst / rozumět. Tento netlist obsahuje informace o použitých buňkách, jejich vzájemném propojení, použité ploše a další podrobnosti. Typické nástroje pro syntézu jsou:

- Cadence RTL Compiler / Build Gates / Physically Knowledgeable Synthesis (PKS)

- Synopsys Design Compiler

Během procesu syntézy jsou aplikována omezení zajišťující, že design splňuje požadovanou funkčnost a rychlost (specifikace). Teprve poté, co je netlist ověřen na funkčnost a načasování, je odeslán pro fyzický návrhový tok.

Kroky

Půdorys

Druhým krokem v toku fyzického návrhu je plánování podlaží . Floorplanning je proces identifikace struktur, které by měly být umístěny blízko sebe, a přidělení prostoru pro ně takovým způsobem, aby splňovaly někdy protichůdné cíle dostupného prostoru (cena čipu), požadovaného výkonu a touhy mít vše blízko na všechno ostatní.

Na základě oblasti návrhu a hierarchie je rozhodnuto o vhodném půdorysu. Plánování podlaží zohledňuje makra použitá v návrhu, paměť, další IP jádra a jejich potřeby umístění, možnosti směrování a také oblast celého návrhu. Plánování podlaží také určuje strukturu IO a poměr stran návrhu. Špatný půdorys povede k plýtvání oblasti matrice a přetížení trasy.

V mnoha metodikách návrhu jsou oblast a rychlost předmětem kompromisů. To je způsobeno omezenými prostředky směrování, protože čím více použitých zdrojů, tím pomalejší operace. Optimalizace pro minimální plochu umožňuje, aby návrh využíval méně zdrojů a aby byl ve větší blízkosti částí návrhu. To vede ke kratším propojovacím vzdálenostem, méně použitým směrovacím prostředkům, rychlejším signálovým cestám end-to-end a ještě rychlejším a konzistentnějším časům míst a tras. Správně, plánování podlah nemá žádné negativy.

Obecným pravidlem je, že sekce datových cest mají největší užitek z plánování podlaží, zatímco náhodnou logiku, stavové automaty a další nestrukturovanou logiku lze bezpečně ponechat v části placeru softwaru místa a trasy.

Datové cesty jsou obvykle oblasti designu, kde se paralelně zpracovává více bitů, přičemž každý bit se upravuje stejným způsobem s možným vlivem sousedních bitů. Příkladem struktur, které tvoří datové cesty, jsou Adders, Subtractors, Counters, Registers, and Muxes.

Rozdělení na oddíly

Rozdělení je proces dělení čipu na malé bloky. Děje se to hlavně k oddělení různých funkčních bloků a také k usnadnění umístění a směrování. Rozdělení lze provést ve fázi návrhu RTL, když návrhář rozdělí celý návrh do dílčích bloků a poté pokračuje v návrhu každého modulu. Tyto moduly jsou vzájemně propojeny v hlavním modulu zvaném modul TOP LEVEL. Tento druh rozdělení se běžně označuje jako logické rozdělení. Cílem rozdělení je rozdělit okruh tak, aby byl minimalizován počet připojení mezi oddíly.

Umístění

Před zahájením optimalizace umístění jsou odstraněny všechny modely zatížení drátem (WLM). Umístění používá k výpočtu načasování hodnoty RC z virtuální trasy (VR). VR je nejkratší vzdálenost mezi dvěma kolíky na Manhattanu. VR RC jsou přesnější než RC WLM.

Umístění se provádí ve čtyřech optimalizačních fázích:

- Optimalizace před umístěním

- V optimalizaci umístění

- Optimalizace po umístění (PPO) před syntézou hodinového stromu (CTS)

- PPO po CTS.

- Optimalizace před umístěním optimalizuje netlist před umístěním, HFN (High Fanout Nets) se sbalí. Může také zmenšit velikost buněk.

- Optimalizace v umístění znovu optimalizuje logiku založenou na VR. To může provádět dimenzování buněk, přesun buněk, přemostění buněk, rozdělení sítě, duplikaci brány, vložení vyrovnávací paměti, obnovení oblasti. Optimalizace provádí iteraci nastavení instalace, přírůstkového načasování a umístění řízeného přetížením.

- Optimalizace po umístění před CTS provede optimalizaci netlistu s ideálními hodinami. Může opravit nastavení, pozastavení, maximální porušení trans / cap. Může provádět optimalizaci umístění na základě globálního směrování. Provádí syntézu HFN.

- Optimalizace po umístění po CTS optimalizuje načasování s rozšířenými hodinami. Snaží se zachovat zkosení hodin.

Syntéza hodinového stromu

Cílem syntézy hodinových stromů ( CTS ) je minimalizovat zkosení a zpoždění vložení. Hodiny se nešíří před CTS, jak je znázorněno na obrázku. Poté, co se CTS přidržení má zlepšit. Strom hodin začíná zdrojem definovaným .sdc a končí stop piny flopu. Existují dva typy zastavovacích kolíků, které se označují jako ignorované kolíky a synchronizační kolíky. Obvody a piny „nedotýkejte se“ na předním konci (logická syntéza) jsou považovány za „ignorovat“ obvody nebo piny na zadním konci (fyzická syntéza). Piny 'Ignorovat' jsou pro analýzu časování ignorovány. Pokud jsou hodiny rozděleny, je nutná samostatná analýza zkosení.

- Globální zkosení dosahuje nulového zkosení mezi dvěma synchronními piny bez ohledu na logický vztah.

- Místní zkosení dosahuje nulového zkosení mezi dvěma synchronními piny při zohlednění logického vztahu.

- Pokud jsou hodiny záměrně zkoseny, aby se zlepšila vůle nastavení, pak se to nazývá užitečné zkosení.

Rigidity je termín vytvořený v Astro, který označuje uvolnění omezení. Čím vyšší je tuhost, tím přísnější jsou omezení.

V rámci optimalizace hodinového stromu (CTO) lze hodiny chránit tak, aby šum nebyl spojen s jinými signály. Stínění ale zvyšuje plochu o 12 až 15%. Protože hodinový signál má globální povahu, stejná kovová vrstva použitá pro směrování energie se používá také pro hodiny. CTO se dosahuje dimenzováním vyrovnávací paměti, dimenzováním brány, přemístěním vyrovnávací paměti, úpravou úrovně a syntézou HFN. Snažíme se vylepšit uvolnění nastavení v předběžném umístění, v optimalizaci umístění a následného umístění před fázemi CTS, přičemž zanedbáváme uvolnění pozastavení. V post placement optimalizace po CTS hold slack je vylepšena. V důsledku CTS je přidáno mnoho vyrovnávacích pamětí. Obecně pro brány 100k je přidáno kolem 650 vyrovnávacích pamětí.

Směrování

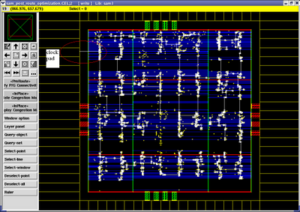

V procesu fyzického návrhu existují dva typy směrování , globální směrování a podrobné směrování. Globální směrování přiděluje prostředky směrování, které se používají pro připojení. Sleduje také přiřazení pro konkrétní síť.

Podrobné směrování provádí skutečná připojení. Během směrování je třeba dbát na různá omezení: DRC, délka drátu, časování atd.

Fyzické ověření

Fyzické ověření kontroluje správnost vygenerovaného návrhu rozložení. To zahrnuje ověření, že rozložení

- Splňuje všechny technologické požadavky - Design Rule Checking (DRC)

- Je v souladu s původním netlistem - Layout vs. Schematic (LVS)

- Nemá žádné anténní efekty - kontrola pravidla antény

- To zahrnuje také ověření hustoty na plné úrovni čipu ... Hustota čištění je velmi důležitým krokem v uzlech nižší technologie

- Splňuje všechny elektrické požadavky - Kontrola elektrických pravidel (ERC).

Zpracování rozvržení

Layout Post Processing, také známá příprava dat masky , často uzavírá fyzický design a ověření. Převádí fyzické rozložení (polygony) na data masky (pokyny pro zapisovatele fotomasek ). To zahrnuje

- Dokončování třísek, jako je vkládání firemních / čipových štítků a finálních struktur (např. Těsnící kroužek, výplňové struktury),

- Generování rozložení záměrného kříže s testovacími vzory a značkami zarovnání,

- Příprava rozložení na masku, která rozšiřuje data rozložení o grafické operace (např. Technologie vylepšení rozlišení , RET) a upravuje data tak, aby maskovala produkční zařízení (zapisovač fotomasek).