POWER6 - POWER6

CPU Power6

| |

| Obecná informace | |

|---|---|

| Spuštěno | 2007 |

| Navrhl | IBM |

| Výkon | |

| Max. Taktovací frekvence CPU | 3,6 GHz až 5,0 GHz |

| Mezipaměti | |

| Mezipaměť L1 | 64+64 KB/jádro |

| Mezipaměť L2 | 4 MB/jádro |

| Mezipaměť L3 | 32 MB/čip (mimo čip) |

| Architektura a klasifikace | |

| Min. velikost funkce | 65 nm |

| Instrukční sada | Power ISA ( Power ISA v.2.05 ) |

| Fyzické specifikace | |

| Jádra | |

| Dějiny | |

| Předchůdce | VÝKON 5 |

| Nástupce | SÍLA 7 |

| Architektury POWER , PowerPC a Power ISA |

|---|

| NXP (dříve Freescale a Motorola) |

| IBM |

|

| IBM/Nintendo |

| jiný |

| Související odkazy |

| Zrušeno šedou barvou , historické kurzívou |

POWER6 je mikroprocesor vyvinutý společností IBM , která implementovala Power ISA v.2.03 . Když byl v roce 2007 k dispozici v systémech, následoval POWER5+ jako vlajkový mikroprocesor Power společnosti IBM. Tvrdí se, že je součástí projektu eCLipz, údajně má za cíl konvergovat serverový hardware IBM tam, kde je to praktické (proto „ipz“ ve zkratce: iSeries , pSeries a zSeries ).

Dějiny

POWER6 byl popsán na mezinárodní konferenci polovodičových obvodů (ISSCC) v únoru 2006 a další podrobnosti byly přidány na fóru mikroprocesorů v říjnu 2006 a na příštím ISSCC v únoru 2007. Formálně bylo oznámeno 21. května 2007. byl vydán 8. června 2007 při rychlostech 3,5, 4,2 a 4,7 GHz, ale společnost uvedla, že prototypy dosáhly 6 GHz. POWER6 dosáhl prvního křemíku v polovině roku 2005 a byl představen na 5,0 GHz v květnu 2008 se zavedením P595.

Popis

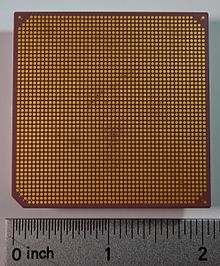

POWER6 je dvoujádrový procesor. Každé jádro je schopné obousměrného simultánního multithreadingu (SMT). POWER6 má přibližně 790 milionů tranzistorů a je velký 341 mm 2 a je vyroben procesem 65 nm . Významným rozdílem oproti POWER5 je, že POWER6 provádí pokyny v pořadí místo mimo pořadí . Tato změna často vyžaduje, aby byl software znovu zkompilován, aby byl zajištěn optimální výkon, ale POWER6 stále dosahuje výrazných vylepšení výkonu oproti POWER5+, a to i u neupraveného softwaru, podle vedoucího inženýra projektu POWER6.

POWER6 také využívá architekturu ViVA-2 , Vi rtual V ector A rchitecture, která umožňuje kombinaci několika uzlů POWER6 fungovat jako jediný vektorový procesor .

Každé jádro má dvě celočíselné jednotky , dvě binární jednotky s plovoucí desetinnou čárkou , jednotku AltiVec a novou jednotku s desetinnou čárkou. Binární jednotka s plovoucí desetinnou čárkou obsahuje podle firemního dokumentu „mnoho mikroarchitektur, logických, obvodových, západkových a integračních technik k dosažení [a] 6cyklového potrubí 13- FO4 “. Na rozdíl od serverů od konkurentů IBM má POWER6 hardwarovou podporu pro desítkovou aritmetiku IEEE 754 a obsahuje první desítkovou jednotku s plovoucí desetinnou čárkou integrovanou v křemíku. Více než 50 nových instrukcí s plovoucí desetinnou čárkou zpracovává desítkovou matematiku a převody mezi binární a desítkovou . Tato funkce byla také přidána do mikroprocesoru z10 v System z10 .

Každé jádro má 64 kB, čtyřcestnou mezipaměť instrukcí pro set-asociativní instrukce a 64 kB datovou cache pro osmicestný set-asociativní design s dvoustupňovým kanálem podporujícím dvě nezávislá 32bitová čtení nebo jedno 64bitové zápisy na cyklus. Každé jádro má polosoukromou 4 MiB unifikovanou mezipaměť L2 , kde ke mezipaměti je přiřazeno konkrétní jádro, ale druhé má k ní rychlý přístup. Obě jádra sdílejí mezipaměť 32 MiB L3, která je vypnutá, pomocí sběrnice 80 GB/s.

POWER6 se může připojit až k 31 dalším procesorům pomocí dvou propojení mezi uzly (50 GB/s) a podporuje až 10 logických oblastí na jádro (až do limitu 254 na systém). K servisnímu procesoru existuje rozhraní, které monitoruje a upravuje výkon a výkon podle nastavených parametrů.

IBM také využívá pro procesor distribuční síť hodin korekce hodin pracovního cyklu 5 GHz. V síti společnost implementuje měděný distribuční vodič o šířce 3 μm a tloušťce 1,2 μm. Konstrukce POWER6 využívá duální napájecí zdroje, logické napájení v rozsahu 0,8 až 1,2 V a napájecí zdroj SRAM o přibližně 150 mV vyšší.

Tepelné charakteristiky POWER6 jsou podobné jako u POWER5 . Doktor Frank Soltis , hlavní vědec IBM, řekl, že IBM vyřešila problémy s únikem energie spojené s vysokou frekvencí použitím kombinace 90 nm a 65 nm částí v konstrukci POWER6.

POWER6+

Mírně vylepšený POWER6+ byl představen v dubnu 2009, ale v systémech Power 560 a 570 byl dodáván od října 2008. Přidal více paměťových klíčů pro bezpečnou paměťovou oblast , což je funkce převzatá z mainframových procesorů IBM .

produkty

Od roku 2008 zahrnuje řada systémů POWER6 modely „Express“ (520, 550 a 560) a Enterprise (570 a 595). Různé modely systémů jsou navrženy tak, aby sloužily jakékoli velikosti podniku. Například 520 Express je prodáván malým podnikům, zatímco Power 595 je prodáván pro velká datová centra s více prostředími. Hlavní rozdíl mezi modely Express a Enterprise spočívá v tom, že tyto modely zahrnují funkce CUoD (Capacity Upgrade on Demand) a „knihy“ procesoru a paměti připojitelné za provozu.

| název | Počet zásuvek | Počet jader | Taktovací frekvence CPU |

|---|---|---|---|

| 520 expres | 2 | 4 | 4,2 GHz nebo 4,7 GHz |

| 550 expres | 4 | 8 | 4,2 GHz nebo 5,0 GHz |

| 560 expres | 8 | 16 | 3,6 GHz |

| 570 | 8 | 16 | 4,4 GHz nebo 5,0 GHz |

| 570 | 16 | 32 | 4,2 GHz |

| 575 | 16 | 32 | 4,7 GHz |

| 595 | 32 | 64 | 4,2 GHz nebo 5,0 GHz |

IBM také nabízí čtyři blade servery založené na POWER6 . Specifikace jsou uvedeny v tabulce níže.

| název | Počet jader | Taktovací frekvence CPU | Vyžadovány otvory pro nože |

|---|---|---|---|

| BladeCenter JS12 | 2 | 3,8 GHz | 1 |

| BladeCenter JS22 | 4 | 4,0 GHz | 1 |

| BladeCenter JS23 | 4 | 4,2 GHz | 1 |

| BladeCenter JS43 | 8 | 4,2 GHz | 2 |

Všechny blade servery podporují AIX, i a Linux. Šasi BladeCenter S a H je podporováno pro blade servery se systémem AIX, i a Linux. Šasi BladeCenter E, HT a T podporuje blade servery se systémem AIX a Linux, ale ne i.

Na konferenci SuperComputing 2007 (SC07) v Renu byl představen nový vodou chlazený Power 575. 575 se skládá z 2U „uzlů“, každý s 32 jádry POWER6 na 4,7 GHz a až 256 GB RAM. Do jednoho rámečku lze nainstalovat až 448 jader.

| název | Počet jader | Taktovací frekvence CPU | Počet ovladačů |

|---|---|---|---|

| DS8700 | 2, 4 | 4,7 GHz | 1, 2 |

| DS8800 | 2, 4, 8 | 5,0 GHz | 1, 2 |

Viz také

- Mikroprocesory IBM POWER

- SÍLA 7

- z10 , sálový procesor, který s POWER6 sdílí mnoho technologií.

Reference

externí odkazy

- Press Kit IBM POWER6

- IBM Power6 zdvojnásobuje rychlost

- „IBM uvolňuje nejrychlejší čip na světě v novém výkonném počítači“ (tisková zpráva). IBM. 21. května 2007.

- InformationWeek report on the Power6nouncement

- Real World Tech, 19. prosince 2005

- InformationWeek, 6. února 2006

- C | Net, 10. října 2006

- Heise Online, 12. října 2006

- Fall Processor Forum 2006: IBM POWER6, Real World Tech, 16. října 2006

- Arstechnica, 19. října 2006

- Arstechnica, 12. února 2007

- Arstechnica, 21. května 2007

Doporučená četba

- POWER Roadmap, IBM, říjen 2006

- MJ Mack; WM Sauer; SB Swaney; BG Mealey (listopad 2007). „Spolehlivost IBM POWER6“. IBM Journal of Research and Development . 51 (6): 763–774. doi : 10,1147/kolo 516,0763 .

- R. Berridge; RM Averill; AE Barish; MA Bowen; PJ Camporese; J. DiLullo; PE Dudley; J. Keinert; DW Lewis; PD Morel; T. Rosser; NS Schwartz; P. Shephard; HH Smith; D. Thomas; PJ Restle; JR Ripley; SL Runyon; PM Williams (listopad 2007). „Fyzický návrh a metodika návrhu mikroprocesoru IBM POWER6“. IBM Journal of Research and Development . 51 (6): 685–714. doi : 10,1147/kolo 516,0685 .

- H. -Y. McCreary; MA Broyles; MS Floyd; AJ Geissler; SP Hartman; FL Rawson; TJ Rosedahl; JC Rubio; MS Ware (listopad 2007). „EnergyScale pro mikroprocesorové systémy IBM POWER6“. IBM Journal of Research and Development . 51 (6): 775–786. doi : 10,1147/kolo 516,0775 .

- MS Floyd; S. Ghiasi; TW Keller; K. Rajamani; FL Rawson; JC Rubio; MS Ware (listopad 2007). „Podpora správy napájení systému v mikroprocesoru IBM POWER6“. IBM Journal of Research and Development . 51 (6): 733–746. CiteSeerX 10.1.1.128.8084 . doi : 10,1147/kolo 516,0733 .

- Velitelství Le; WJ Starke; Pole JS; FP O'Connell; DQ Nguyen; BJ Ronchetti; WM Sauer; EM Schwarz; MT Vaden (listopad 2007). „Mikroarchitektura IBM POWER6“. IBM Journal of Research and Development . 51 (6): 639–662. CiteSeerX 10.1.1.115.6020 . doi : 10,1147/kolo 516,0639 .

- DW Plass; YH Chan (listopad 2007). „Pole IBM POWER6 SRAM“. IBM Journal of Research and Development . 51 (6): 747–756. doi : 10,1147/kolo 516,0747 .

- L. Eisen; JW Ward; H. -W. Ochutnávka; N. Mading; J. Leenstra; SM Mueller; C. Jacobi; J. Preiss; EM Schwarz; SR Carlough (listopad 2007). „Akcelerátory IBM POWER6: VMX a DFU“. IBM Journal of Research and Development . 51 (6): 1–21. CiteSeerX 10.1.1.128.3776 . doi : 10,1147/kolo 516,0663 .

- „POWER: Šestá generace“. (30. října 2006). Zpráva o mikroprocesoru .