Texas Instruments TMS9900 - Texas Instruments TMS9900

| Návrhář | Texas Instruments |

|---|---|

| Bity | 16bitové |

| Představeno | 1976 |

| Design | CISC |

| Endianness | Velký |

| Registry | |

| PC, WP, ST | |

| Obecný účel | 2 interně umístěné v procesoru (WP, ST) 16 × 16bitový zásobník umístěný v externí RAM |

TMS9900, představený v červnu 1976, byl jedním z prvních komerčně dostupných jednočipových 16bitových mikroprocesorů . Je realizován Texas Instruments " TI-990 minipočítač architekturu ve formátu single-chip, a byl původně používán pro low-end modely této nastoupit.

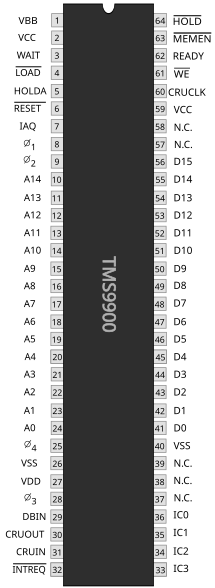

Jeho 64pinový formát DIP způsobil, že implementace v menších strojích byla dražší než běžnější 40pinový formát, a mimo vlastní použití TI viděl relativně málo vítězství v designu. Mezi tato použití patřil domácí počítač TI-99/4 společnosti TI , který se nakonec prodal asi ~ 2,8 milionu příkladů.

V polovině 80. let se pole mikropočítačů přesouvalo na 16bitové systémy jako Intel 8088 a novější 16/32bitové designy jako Motorola 68000 , které snadno překonaly 9900 a byly obecně méně nákladné. Bez zjevné budoucnosti čipu se společnost TI zaměřila na speciální procesory, jako je Texas Instruments TMS320 , představený v roce 1983.

Dějiny

TMS9900 byl navržen jako jednočipová verze řady minipočítačů TI 990 , podobně jako Intersil 6100 byl jednočipový PDP-8 (12 bitů) a Fairchild 9440 a Data General mN601 byly jednočipové verze Data General je Nova . Na rozdíl od vícečipových 16bitových mikroprocesorů, jako je National Semiconductor IMP-16 nebo DEC LSI-11 , z nichž některé byly starší než TMS9900, byl tento druhý jednočipový, samostatný 16bitový mikroprocesor. Jediný známý jednočipový 16bitový design, který předchází TMS9900, je téměř neznámý Panafacom MN1610 , vydaný v roce 1975.

Kořeny minipočítačů TMS9900 vedou k řadě architektonických prvků, které se u návrhů, které začaly z prázdného listu, běžně nevyskytují. Mezi nimi bylo pozoruhodné použití registrů TMS9900, které jsou mapovány do hlavní paměti . To umožňuje rychlé přepínání kontextu , kterého lze dosáhnout změnou jediného ukazatele, zatímco tradičnější návrhy by vyžadovaly uložení celé sady interních registrů do paměti nebo zásobníku. Temnější stránkou tohoto přístupu je, že přístup k těmto registrům je časově náročnější. V implementaci minipočítače je efekt relativně malý a vzestup v prostředí s více úkoly je významný. V jiných rolích, jako jsou mikropočítače pro jednoho uživatele nebo vestavěné systémy, se tento kompromis nemusí vyplatit.

Společnost TI používala pro podnikovou synergii stejnou architekturu napříč různými divizemi: „jedna společnost, jedna počítačová architektura“. Koncem 70. let Walden C. Rhines představil TMS9900 skupině IBM vyvíjející osobní počítač. „Do roku 1981 bychom nevěděli, co jsme ztratili“, protože IBM si pro počítač IBM vybral Intel 8088 , vzpomínal. Po neúspěšném pokusu dostat se na trh osobních počítačů s produkty, jako je TI-99/4A , divize mikroprocesorů společnosti nakonec přešla na řadu speciálních procesorů TMS320 .

Architektura

TMS9900 má tři interní 16bitové registry - čítač programů (PC), stavový registr (ST) a registr ukazatele pracovního prostoru (WP). Register WP ukazuje na základní adresu v externí RAM, kde je uloženo 16 obecných uživatelských registrů procesoru (každý o šířce 16 bitů). Tato architektura umožňuje rychlé přepínání kontextu ; např. když je zadán podprogram, je třeba změnit pouze jeden registr pracovního prostoru místo toho, aby bylo nutné ukládat registry jednotlivě.

Adresy odkazují na bajty s konvencí uspořádání velkých endianů . TMS9900 je klasický 16bitový stroj s adresním prostorem 2 16 bajtů (65 536 bajtů nebo 32 768 slov).

Neexistuje žádný koncept zásobníku a žádný registr ukazatele zásobníku. Místo toho existují instrukce větve, které uloží čítač programu do registru a změní kontext registru. 16 hardwarových a 16 softwarových vektorů přerušení se skládá z dvojice hodnot PC a WP, takže přepnutí kontextu registru je automaticky prováděno také přerušením.

Sada instrukcí a adresování

TMS9900 má 69 instrukcí, které jsou dlouhé jedno, dvě nebo tři slova a vždy jsou v paměti zarovnány se slovy. Sada instrukcí je poměrně ortogonální , což znamená, že až na několik výjimek mohou instrukce používat všechny metody přístupu k operandům (režimy adresování).

Režimy adresování zahrnují Immediate (operand v instrukci), Direct nebo „Symbolic“ (adresa operandu v instrukci), Register (operand v registru pracovního prostoru), Register Indirect (adresa operandu v registru pracovního prostoru) s nebo bez automatického přírůstku, Indexované (adresa operandu) v instrukci indexované s obsahem registru pracovního prostoru) a Program Counter Relative.

Nejdůležitější instrukce se dvěma operandy (sčítání, odčítání, porovnávání, přesun atd.) Obsahují 2bitový režim adresování a pole pro výběr 4bitového registru pro zdrojové i cílové operandy. V operačním kódu je režim "Symbolický" reprezentován jako indexovaný režim s registrovým polem nastaveným na 0, proto registr pracovního prostoru 0 (WR0) nelze použít v indexovaném režimu. V méně často používaných instrukcích se dvěma operandy, jako je XOR, musí být cílovým operandem registr pracovního prostoru (nebo pár registru pracovního prostoru v případě instrukcí násobení a dělení).

Řízení toku je usnadněno prostřednictvím skupiny jednoho bezpodmínečného a dvanácti podmíněných skokových instrukcí. Cíle skoků jsou relativní k PC s offsetem -128 až +127 slovních adres.

U podprogramových volání instrukce BLWP (Branch and Load Workspace Pointer) načte nové hodnoty WP a PC a poté uloží hodnoty WP, PC a ST do (nových) registrů 13, 14 a 15. Na konci podprogramu je ukazatel pracovního prostoru návratu (RTWP) obnoví v opačném pořadí. Pomocí BLWP/RTWP je možné vnořovat volání podprogramů navzdory absenci zásobníku, ale programátor musí explicitně přiřadit příslušný pracovní prostor registru.

Sada instrukcí také obsahuje operační kód Branch and Link (BL), který ukládá počítač pouze k registraci 11 bez změny WP. V tomto případě může jako návratový operační kód sloužit instrukce větve (B) používající jako cílovou adresu WR11, ale podprogramy typu BL nelze vnořit, aniž by programátor provedl akce k uložení návratové adresy.

TMS9900 podporuje instrukci ke spuštění „X“ (eXecute). Tato instrukce provede instrukci v registru. Lze jej použít k ladění (jako instrukce zarážky ) a k vytváření tabulek indexovaných operačních kódů, jak se používají v interpretech bajtového kódu.

TMS9900 také podporuje instrukci eXtended OPeration (XOP). XOP má číslo v rozsahu 0-15 a také zdrojovou adresu. Při vyvolání instrukce provede přepnutí kontextu prostřednictvím jednoho ze šestnácti vektorů na předdefinovaných místech v paměti. Je to podobné přerušení, ale instrukce XOP také ukládá zdrojovou adresu do registru 11 nového pracovního prostoru. XOP je méně flexibilní než BLWP, protože přenosové vektory musí být na pevných místech, ale šetří paměť, protože zdrojovou adresu může místo toho použít provedený podprogram, když nedefinuje umístění vektoru. XOP se používá k implementaci pokynů v softwaru v modelech nižší kategorie, kde vyšší verze minipočítačů řady 990 mohou mít k jejich provedení vyhrazený hardware.

V typickém srovnání s Intel 8086 měl TMS9900 menší programy. Jedinou nevýhodou byl malý adresní prostor a potřeba rychlé RAM.

Implementace

TMS9900 byl implementován v N-kanálovém procesu MOS křemíkové brány, který vyžadoval napájecí zdroje +5 V, −5 V a +12 V a čtyřfázové (nepřekrývající se) hodiny s maximální frekvencí 3 MHz (333 ns cyklus), obvykle generovaný ze 48 MHz krystalu pomocí čipu generátoru hodin TIM9904 (aka 74LS362).

Nejkratší instrukce vyžadují k dokončení osm hodinových cyklů nebo 2,7 μs (za předpokladu 0 externích čekacích cyklů), mnoho dalších běží mezi 10 a 14 cykly (3,3 ... 4,7 μs); nejdéle trvající instrukce (DIV) může trvat až 124 cyklů (41,3 μs).

Čip byl zabalen do (tehdy neobvyklého) 64kolíkového, 0,9 "širokého DIP . Poměrně velký počet pinů umožňoval vyvedení 15bitové (slovní) adresové sběrnice a 16bitové datové sběrnice na vyhrazené piny bez použití multiplexování (na rozdíl např. od procesoru Intel 8086 ), zachování jednoduchosti připojení externí paměti. Na rozdíl od konvence používané mnoha jinými výrobci označil TI nejvýznamnější adresové a datové řádky „A0“ a „D0“. datové cesty a ALU jsou 16 bitů široké.

Procesor lze pozastavit s adresovou sběrnicí uvedenou pro externí přímý přístup do paměti (DMA). Přístupy do paměti jsou vždy široké 16 bitů, přičemž CPU pro přístupy v celém bajtu automaticky provádí operace čtení před zápisem.

Hardwarový systém přerušení podporuje 4bitový prioritní vstup přerušení, který musel být vyšší než úroveň priority uložená ve stavovém registru (bity 12–15), aby mohla být žádost o přerušení obsloužena. Kromě toho, / LOAD vstup poskytuje NMI zařízení s vyhrazeným vektoru.

CPU TMS9900 také obsahuje 16bitový posuvný registr („CRU“) navržený pro propojení s externími posuvnými registry, s vyhrazenými instrukcemi podporujícími přístup do polí o šířce 1–16 bitů z celkem 4096 adresovatelných bitů.

Paralelní periferie mohou být připojeny způsobem mapovaným v paměti k běžné adrese a datové sběrnici.

Aplikace

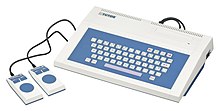

TMS9900 byl použit v domácích počítačích TI-99/4 a TI-99/4A . Aby se snížily výrobní náklady, TI se bohužel rozhodl použít v těchto systémech pouze 128 16bitových slov rychlého typu RAM, ke kterému měl TMS9900 přímý přístup. Zbytek paměti byl 16 kB 8bitové paměti DRAM, která byla přístupná pouze nepřímo prostřednictvím řadiče zobrazení videa, což ochromilo výkon TI-99/4.

TI vyvinul řadu počítačových modulů TM990, včetně CPU, paměti, I/O, které po zapojení do rámečku karty mohly tvořit 16bitový minipočítač. Ty se obvykle používaly pro řízení procesů. Byl vydán mikroprocesorový trenér ve formě TM990/189.

Vývoj rodinného produktu TMS9900

Druhou generací rodiny mikroprocesorů TMS9900 byl TMS9995, který poskytoval „funkční výkon při rychlostech 3krát rychlejších než jakýkoli předchozí procesor řady 9900“, a to především díky začlenění technologie předběžného načítání instrukcí. V domácí počítačové aréně našel TMS9995 využití pouze v Tomy Tutor , esoterickém upgradu TI99-4/A s názvem Geneve 9640 a projektu vytištěném v časopise Electronics Today : Powertran Cortex. Bylo plánováno, že bude použit v počítačových systémech TI-99/2 a TI-99/8, ale ani pokročilé přes fázi prototypu.

TI později vyvinul výkonnější rodinu mikroprocesorů TMS99000, která byla použita jako CPU v minipočítači 990/10A jako snížení nákladů. Bohužel v době, kdy se 990/10A dostala na trh, byl konec minipočítačové éry již na dohled.

Rodina TMS99000 zahrnuje dva mikroprocesory, TMS99105A a TMS99110A, které jsou identické s výjimkou zahrnutí paměti ROM na čipu macrostore ROM (paměť macrostore obsahuje přidané funkce nebo instrukce prostřednictvím rutin emulace zapsaných ve standardním strojovém kódu). Macrostore ROM na mikroprocesoru TMS99110A na čipu obsahuje instrukce s plovoucí desetinnou čárkou, které jsou k dispozici jako součást sady instrukcí pro jazyk stroje, zatímco TMS99105A neobsahuje makrostore ROM. Byl oznámen třetí člen rodiny TMS99000, TMS99120, ale nikdy nebyl komerčně vyráběn. ROM Macrostore na čipu v TMS99120 obsahuje rutiny podpory běhu pro jazyk PASCAL na vysoké úrovni.

Sada instrukcí pro rodinu TMS99000 je nadmnožinou modelů TMS9995 a TMS9900 s kompatibilitou objektového kódu. Další pokyny zahrnují pokyny pro násobení a dělení se znaménkem; posunutí dlouhého slova, sčítání a odčítání; registr stavu zatížení, ukazatel zatížení pracoviště, operace zásobníku, podpora více procesorů, manipulace s bitem. Členové rodiny mají okamžitý přístup k 256 kB paměti a mohou použít mapovač paměti TIM99610 k adresování až 16 MB. Architektura obsahuje mnoho dalších vylepšení oproti TMS9900 a TMS9995.

Varianty

| Modelka | Popis |

|---|---|

| TI990/9 | Early multi-chip CPU for minicomputer systems, 1974 |

| TI990/10 | Implementace více čipů pro minipočítačové systémy, 1975 |

| TI990/12 | Implementace více čipů, rychlejší než 990/10 |

| TMS9900 | Implementace jednoho čipu, 1976, použitá v počítači TI-99/4 (A) |

| TMS9940 | Mikrokontrolér s 2 kB ROM, 128 B RAM, snižovač, sběrnice CRU, 1979 |

| TMS9980 TMS9981 |

8bitové verze TMS9900 |

| TMS9985 | TMS9940 s 8 kB ROM, 256 B RAM a 8bitovou externí sběrnicí, c. 1978 (nikdy nevydáno) |

| TMS9989 | Vylepšeno 9980, používané ve vojenském hardwaru |

| TMS9995 | Vylepšeno jako TMS9985, žádná ROM. Používá se v prototypech TI-99/2 a TI-99/8, počítači Tomy Tutor a Geneve |

| TMS99105 | Základní člen rodiny mikroprocesorů TMS99000 |

| TMS99110 | Mikroprocesor rodiny TMS99000 s instrukcemi s plovoucí desetinnou čárkou předprogramovaný do paměti ROM Macrostore na čipu |

| TMS99120 | Mikroprocesor rodiny TMS99000 s rutinami podpory běhu pro jazyk PASCAL na vysoké úrovni předprogramovaný do paměti ROM Macrostore na čipu (mikroprocesor byl oznámen, ale možná nikdy nebyl komerčně vyráběn) |

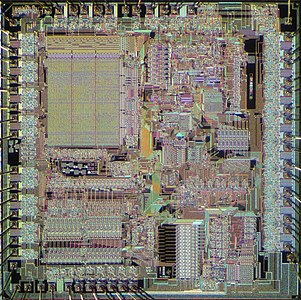

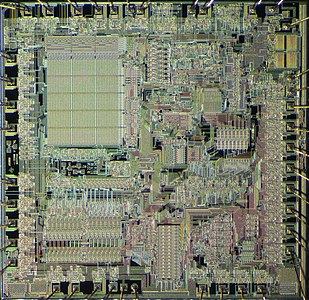

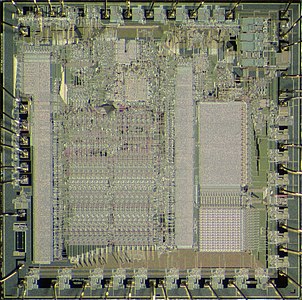

- Zemřít fotografie

Reference

externí odkazy

- Manuály TMS9900 a reference od Bitsavers