Transputer - Transputer

Transputerová je řada průkopníkem mikroprocesory od 1980, zahrnující integrovanou paměť a sériové komunikační spojení, které jsou určeny pro paralelní výpočty . Byly navrženy a vyrobeny společností Inmos , polovodičovou společností se sídlem v Bristolu ve Velké Británii .

Nějakou dobu na konci osmdesátých let mnozí považovali transputer za další skvělý design pro budoucnost výpočetní techniky. Zatímco Inmos a transputer tohoto očekávání nedosáhli, architektura transputeru měla velký vliv při vyvolávání nových myšlenek v počítačové architektuře , z nichž některé se v moderních systémech znovu objevily v různých formách.

Pozadí

Na začátku 80. let 20. století se zdálo , že konvenční centrální procesorové jednotky (CPU) dosahují výkonnostního limitu. Do té doby výrobní potíže omezovaly množství obvodů, které se vešly na čip. Pokračující vylepšení v procesu výroby však toto omezení odstranilo. Během deseti let mohly čipy pojmout více obvodů, než jak konstruktéři věděli použít. Tradiční návrhy počítačů s komplexními instrukčními sadami (CISC) dosahovaly výkonnostní úrovně a nebylo jasné, zda je lze překonat.

Zdálo se, že jedinou cestou vpřed je zvýšit používání paralelismu, využití několika CPU, které by spolupracovaly na řešení několika úkolů současně. To záviselo na tom, že takové stroje dokážou spustit několik úkolů najednou, což je proces nazývaný multitasking . To bylo obecně příliš obtížné pro předchozí návrhy CPU zvládnout, ale novější návrhy to dokázaly efektivně dosáhnout. Bylo jasné, že v budoucnu to bude funkce všech operačních systémů (OS).

Vedlejším efektem většiny multitaskingových návrhů je, že často také umožňuje spouštění procesů na fyzicky odlišných CPU, v takovém případě se tomu říká multiprocesing . Levný procesor postavený pro vícenásobné zpracování by mohl umožnit zvýšení rychlosti stroje přidáním více procesorů, potenciálně mnohem levněji než použitím jednoho rychlejšího návrhu CPU.

První návrhy transputerů byly způsobeny počítačovým vědcem Davidem Mayem a telekomunikačním poradcem Robertem Milnem. V roce 1990 obdržel May čestný titul DSc z University of Southampton , v roce 1991 následovalo jeho zvolení za člena Královské společnosti a v roce 1992 ocenění Pattersonovy medaile z Fyzikálního ústavu . Tony Fuge , tehdejší vedoucí inženýr Inmosu , byl v roce 1987 oceněn Cenou prince Philipa za jeho práci na transputeru T414.

Design

Transputerová (název vyplývá z „ trans istor“ a „com Puter “) byl první obecný účel mikroprocesor navržen speciálně pro použití v paralelních výpočetních systémů. Cílem bylo vyrobit rodinu čipů o výkonu a nákladech, které by bylo možné propojit dohromady a vytvořit tak úplný paralelní počítač. Název byl vybrán, aby naznačoval roli, kterou budou hrát jednotlivé transputery: jejich počet bude použit jako základní stavební kameny, stejně jako dříve tranzistory .

Původně byl plán, aby transputer stál jen pár dolarů za jednotku. Inmos viděl, že jsou používány prakticky ke všemu, od provozu jako hlavního CPU pro počítač až po funkci kanálového řadiče pro diskové jednotky ve stejném počítači. V tradičním počítači by byla například schopnost procesoru řadiče disku nečinná, pokud by se k disku nepřistupovalo. Naproti tomu v transputerovém systému mohly být náhradní cykly na kterémkoli z těchto transvertorů použity pro jiné úkoly, což výrazně zvýšilo celkový výkon strojů.

I jeden transputer bude mít všechny obvody potřebné k práci sám, což je funkce, která je běžněji spojována s mikrokontroléry . Záměrem bylo umožnit co nejjednodušší propojení transputerů bez potřeby složité sběrnice nebo základní desky . Bylo nutné dodat napájení a jednoduchý hodinový signál , ale nic jiného: vestavěná paměť s náhodným přístupem (RAM), řadič RAM, podpora sběrnice a dokonce i operační systém v reálném čase (RTOS).

Architektura

Původní transputer používal velmi jednoduchou a dosti neobvyklou architekturu k dosažení vysokého výkonu na malé ploše. Jako hlavní způsob ovládání datové cesty používal mikrokód , ale na rozdíl od jiných návrhů té doby provedení mnoha instrukcí trvalo jen jeden cyklus. Jako vstupní body do paměti jen pro čtení mikrokódu (ROM) byly použity instrukční operační kódy a výstupy z ROM byly přiváděny přímo do datové cesty. U instrukcí s více cykly, zatímco datová cesta prováděla první cyklus, mikrokód dekódoval čtyři možné možnosti pro druhý cyklus. Rozhodnutí, která z těchto možností bude skutečně použita, by mohlo být učiněno blízko konce prvního cyklu. To umožnilo velmi rychlý provoz při zachování obecné architektury.

Taktovací frekvence 20 MHz byla poměrně vysoká pro éru a designéři byli velmi znepokojen praktičnosti distribuci takovou rychlou hodinový signál na palubě. Byl použit pomalejší externí takt 5 MHz, který byl znásoben na potřebnou vnitřní frekvenci pomocí smyčky fázového závěsu (PLL). Interní hodiny ve skutečnosti měly čtyři nepřekrývající se fáze a konstruktéři mohli libovolně používat jejich kombinaci, takže bylo možné tvrdit, že transputer ve skutečnosti běžel na 80 MHz. Dynamická logika byla použita v mnoha částech návrhu ke snížení plochy a zvýšení rychlosti. Tyto metody se bohužel obtížně kombinují s testováním generování skenování generováním automatického testovacího vzoru, takže pro pozdější návrhy upadly v nemilost.

Prentice-Hall vydal knihu o obecných principech transputeru.

Odkazy

Základní konstrukce transputeru obsahovala sériové linky známé jako „os-link“, které mu umožňovaly komunikovat až se čtyřmi dalšími transputery, každý rychlostí 5, 10 nebo 20 Mbit/s-což bylo v osmdesátých letech velmi rychlé. Přes odkazy (které by mohly běžet desítky metrů) bylo možné spojit libovolný počet transputerů a vytvořit tak jednu výpočetní farmu . Hypotetický stolní počítač může mít dva z „low end“ transputerů zpracovávajících vstupně/výstupní (I/O) úkoly na některých svých sériových linkách (napojených na příslušný hardware), zatímco hovoří s jedním ze svých větších bratranců fungujícím jako CPU na jiném.

Velikost systému, který lze tímto způsobem vybudovat, byla omezena. Protože každý transputer byl propojen s jiným v pevném uspořádání bod-bod, odesílání zpráv na vzdálenější transputer vyžadovalo, aby zprávy byly přenášeny každým čipem v řádku. To zavedlo zpoždění při každém „přeskakování“ přes odkaz, což vedlo k velkým zpožděním na velkých sítích. K vyřešení tohoto problému poskytl Inmos také přepínač s nulovým zpožděním, který připojil až 32 převodníků (nebo přepínačů) do ještě větších sítí.

Bootování

Transputery se mohly spouštět z paměti, jako je tomu u většiny počítačů, ale mohly být také spuštěny přes jeho síťová spojení . Speciální pin na čipech, BootFromROM, naznačil, jakou metodu má použít. Pokud byl při resetování čipu uplatněn BootFromROM, zahájil by zpracování podle instrukcí dva bajty z horní části paměti, které se normálně používaly k provedení zpětného skoku do bootovacího kódu. Pokud by tento pin nebyl uplatněn, čip by místo toho čekal na přijetí bajtů na jakémkoli síťovém připojení. První bajt, který měl být přijat, byla délka kódu, který se měl dodržovat. Následující bajty byly zkopírovány do nízké paměti a poté přeskočeny, jakmile byl přijat počet bajtů.

Obecným konceptem systému bylo mít jeden transputer jako ústřední orgán pro zavedení systému obsahujícího několik připojených transputerů. Vybraný transputer by měl trvale potvrzený BootFromROM, což by způsobilo, že při spuštění spustí proces spouštění z ROM. Ostatní transputery by měly BootFromROM vázané nízko a jednoduše by čekaly. Zavaděč by spustil centrální transputer, který by poté začal odesílat zaváděcí kód na ostatní transputery v síti, a mohl by kód odeslaný každému z nich přizpůsobit, například odesláním ovladače zařízení do transputeru připojeného k pevným diskům.

Systém také zahrnoval „speciální“ délky 0 a 1, které byly vyhrazeny pro PEEK a POKE . To umožnilo kontrolu a změnu paměti RAM v nezavedeném transputeru. Po nahlédnutí následovaném adresou paměti nebo poke s adresou a jediným slovem dat se transputer vrátí k čekání na bootstrap. Tento mechanismus byl obecně používán pro ladění.

Plánovač

Přes odkazy byl přidán plánovaný provoz obvodů. Procesy čekající na komunikaci se automaticky pozastaví, zatímco síťové obvody dokončily čtení nebo zápis. Ostatní procesy běžící na transputeru by pak měly daný čas zpracování. Obsahuje dvě úrovně priority pro zlepšení provozu v reálném čase a více procesorů . Ke komunikaci mezi programy běžícími na jednom transputeru byl použit stejný logický systém, implementovaný jako odkazy virtuální sítě v paměti. Programy požadující jakýkoli vstup nebo výstup se automaticky pozastavily, když byla operace dokončena, což je úkol, který normálně vyžadoval, aby operační systém zvládl jako arbitr hardwaru. Operační systémy na transputeru nemusely zvládat plánování; dalo by se předpokládat, že čip má uvnitř OS.

Instrukční sada

Aby byla všechna tato funkce obsažena na jednom čipu, byla základní logika transputeru jednodušší než většina procesorů. Zatímco někteří to nazývali počítačem se sníženou instrukcí (RISC) kvůli jeho poměrně řídké povaze, a protože to bylo tehdy žádoucí marketingové heslo , bylo silně mikrokódované , mělo omezenou sadu registrů a komplexní instrukce z paměti do paměti. z nichž jej pevně umístit do tábora CISC . Na rozdíl od CPU RISC s velkým zatížením/ukládáním měl transputer pouze tři datové registry, které se chovaly jako zásobník. Ukazatel pracovního prostoru navíc ukazoval na konvenční zásobník paměti, snadno přístupný pomocí pokynů Load Locala Store Local. To umožnilo velmi rychlé přepínání kontextu jednoduše změnou ukazatele pracovního prostoru na paměť používanou jiným procesem (metoda používaná v řadě současných návrhů, jako je TMS9900 ). Obsah tří registrů nebyl zachován podle určitých instrukcí, jako je Jump, když transputer mohl provést přepnutí kontextu.

Souprava transputerová pokyn se skládala z 8-bitových instrukcí sestavených z opcode a operandů křupky . Horní okusovat obsahovala 16 možných primární instrukční kódy, což je jeden z mála komercializace minimální instrukční sadu počítače . Nižší nibble obsahoval jeden bezprostřední konstantní operand, běžně používané jako offset vzhledem k ukazateli pracovního prostoru (paměť zásobník). Dvě instrukce prefixu umožňovaly konstrukci větších konstant tím, že se jejich spodní kousky připravily na operandy následujících pokynů. Další instrukce byly podpořeny prostřednictvím instrukčního kódu Operate ( Opr), který dekódoval konstantní operand jako rozšířený operační kód s nulovým operandem, což zajišťovalo téměř nekonečné a snadné rozšiřování sady instrukcí, protože byly zavedeny novější implementace transputeru.

16 'primárních' instrukcí o jednom operandu bylo:

| Mnemotechnická pomůcka | Popis |

|---|---|

| J. | Skok - přidejte okamžitý operand do ukazatele instrukce |

| LDLP | Načíst místní ukazatel-načte ukazatel relativní k pracovnímu prostoru na začátek zásobníku registrů |

| PFIX | Předpona - obecný způsob, jak zvýšit dolní část následující primární instrukce |

| LDNL | Načíst nelokální-načte posunutí hodnoty od adresy v horní části zásobníku |

| LDC | Načíst konstantu - načte operand konstanty na začátek zásobníku registrů |

| LDNLP | Načíst nelokální ukazatel-načíst adresu, odsazeno od vrcholu zásobníku |

| NFIX | Negativní předpona - obecný způsob, jak negovat (a případně zvýšit) nižší okusování |

| LDL | Načíst místní - načtení hodnoty offsetu z pracovního prostoru |

| ADC | Přidat konstantu - přidá konstantní operand na začátek zásobníku registrů |

| VOLÁNÍ | Volání podprogramu - stiskněte ukazatel instrukce a skočte |

| CJ | Podmíněný skok - v závislosti na hodnotě v horní části zásobníku registrů |

| AJW | Upravit pracovní prostor - přidejte operand do ukazatele pracovního prostoru |

| EQC | Rovná se konstantě - otestujte, zda se vrchol zásobníku registrů rovná konstantnímu operandu |

| STL | Místní úložiště - ukládejte v neustálém odsazení od pracovního prostoru |

| STNL | Store non-local-store at address offset from top of stack |

| OPR | Operate - obecný způsob rozšíření sady instrukcí |

Všechny tyto instrukce mají konstantu, která představuje offset nebo aritmetickou konstantu. Pokud byla tato konstanta menší než 16, všechny tyto instrukce byly kódovány do jednoho bajtu.

Prvních 16 'sekundárních' instrukcí s nulovým operandem (pomocí primární instrukce OPR) bylo:

| Mnemotechnická pomůcka | Popis |

|---|---|

| REV | Obrátit - prohoďte dvě horní položky zásobníku registrů |

| LB | Načíst bajt |

| BSUB | Bajtový dolní index |

| ENDP | Ukončit proces |

| DIFF | Rozdíl |

| PŘIDAT | Přidat |

| GCALL | Obecné volání - prohoďte horní část zásobníku a ukazatel instrukcí |

| V | Vstup - příjem zprávy |

| PROD | Produkt |

| GT | Větší než - jediná srovnávací instrukce |

| WSUB | Dolní index slov |

| VEN | Výstup - odeslání zprávy |

| SUB | Odčítat |

| STARTP | Spusťte proces |

| DOSTATEK | Výstupní bajt-odeslání jednobajtové zprávy |

| OUTWORD | Výstupní slovo-odeslání jednoslovné zprávy |

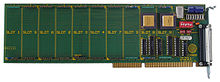

Rozvoj

Poskytují snadný prostředek prototyping, konstrukci a konfiguraci více Transputer systémy, Inmos představil TRAM (Transputer modul) standard v roce 1987. tramvaji byl v podstatě stavební blok daughterboard zahrnující Transputer a, volitelně, externí paměť a / nebo periferní zařízení, s jednoduchými standardizovanými konektory poskytujícími napájení, transputerové odkazy, hodinové a systémové signály. Byly definovány různé velikosti TRAM, od základní TRAM velikosti 1 (3,66 palce o 1,05 palce) až po velikost 8 (3,66 palce o 8,75 palce). Inmos vyrobil řadu základních desek TRAM pro různé hostitelské sběrnice, jako je Industry Standard Architecture (ISA), MicroChannel nebo VMEbus . Spoje TRAM pracují s rychlostí 10 Mbit/s nebo 20 Mbit/s.

Software

Transputery byly určeny k programování pomocí programovacího jazyka occam na základě procesního počtu komunikačních sekvenčních procesů (CSP) . Transputerová byl postaven pro spuštění Occamova specificky, více než současných CISC designy byly postaveny běžet jazyky jako Pascal nebo C . Occam podporoval souběžnou a kanálovou meziprocesovou nebo meziprocesorovou komunikaci jako základní součást jazyka. S paralelismem a komunikací zabudovanou v čipu a s jazykem, který s ním přímo interaguje, se psaní kódu pro věci, jako jsou ovladače zařízení, stalo trivialitou; i ten nejzákladnější kód mohl sledovat sériové porty pro I/O a automaticky by spal, když nebyla žádná data.

Počáteční vývojové prostředí Occam pro transputer byl Inmos D700 Transputer Development System (TDS). Jednalo se o neortodoxní integrované vývojové prostředí zahrnující editor, kompilátor, linker a (post-mortem) debugger. TDS byla transputerová aplikace napsaná v Occam. Textový editor TDS byl pozoruhodný v tom, že to byl skládací editor , který umožňoval skrytí a odhalení bloků kódu, aby byla struktura kódu zjevnější. Bohužel kombinace neznámého programovacího jazyka a stejně neznámého vývojového prostředí neudělala nic pro ranou popularitu transputeru. Později Inmos vydá více konvenčních křížových kompilátorů Occam, sady nástrojů Occam 2 .

Implementace více hlavních programovacích jazyků, jako jsou C, FORTRAN , Ada a Pascal, byly také později vydány jak Inmosem, tak dodavateli třetích stran. Ty obvykle zahrnovaly jazyková rozšíření nebo knihovny poskytující méně elegantním způsobem souběžnost podobnou Occamu a kanálovou komunikaci.

Nedostatek podpory transputeru pro virtuální paměť znemožnil portování běžných variant operačního systému Unix , přestože byly vyrobeny porty operačních systémů podobných Unixu (například Minix a Idris od Whitesmiths ). Pokročilý distribuovaný operační systém podobný Unixu , HeliOS , byl také navržen speciálně pro systémy s více transputery společností Perihelion Software .

Implementace

První transputery byly oznámeny v roce 1983 a vydány v roce 1984.

V souladu se svou rolí zařízení podobných mikrokontrolérům obsahovali integrovanou RAM a vestavěný řadič RAM, který umožňoval přidání větší paměti bez přidaného hardwaru. Na rozdíl od jiných návrhů transputery neobsahovaly I/O linky: ty měly být přidány s hardwarem připojeným ke stávajícím sériovým linkám. Existovala jedna řada „Událost“, podobná linii přerušení konvenčního procesoru. Program, který je považován za kanál, může „vstupovat“ z kanálu událostí a pokračovat až po uplatnění řádku událostí.

Všechny převodníky běžely z externího hodinového vstupu 5 MHz; toto bylo znásobeno, aby poskytlo hodiny procesoru.

Transputer neobsahoval jednotku pro správu paměti (MMU) ani systém virtuální paměti .

Varianty transputeru (kromě zrušeného T9000) lze rozdělit do tří skupin: 16bitová řada T2 , 32bitová řada T4 a 32bitová řada T8 s 64bitovou podporou plovoucí desetinné čárky IEEE 754 .

T2: 16bitové

Prototypem 16bitového transputeru byl S43 , kterému na spojích chyběl plánovač a blokový přenos řízený DMA. Při spuštění byly T212 a M212 (druhý s integrovaným diskovým řadičem) 16bitovými nabídkami. T212 byl k dispozici v hodnocení rychlosti procesoru 17,5 a 20 MHz. T212 byl nahrazen T222 , s on-chip RAM rozšířen od 2 KB na 4 KB, a později na T225 . To přidalo podporu ladění- zarážky (rozšířením instrukce "J 0") plus nějaké další instrukce z instrukční sady T800. T222 i T225 běžely na 20 MHz.

T4: 32bitový

Při spuštění byl T414 32bitovou nabídkou. Původně měl být první 32bitovou variantou T424 , ale potíže s výrobou znamenaly, že byl přepracován na T414 s 2 KB palubní RAM namísto předpokládaných 4 KB. T414 byl k dispozici v 15 a 20 MHz variantách. RAM byla později obnovena na 4 KB na T425 (u variant 20, 25 a 30 MHz), což také přidaloJ 0podpora zarážky a další pokyny pro T800. T400 , vydaná v září 1989, byl nízkonákladový 20 MHz T425 derivát s 2 KB a dva namísto čtyř vazeb, které jsou určeny pro vestavěných systémů trhu.

T8: plovoucí desetinná čárka

Transputer T800 druhé generace , představený v roce 1987, měl rozšířenou sadu instrukcí. Nejdůležitějším přírůstkem byla 64bitová jednotka s plovoucí desetinnou čárkou (FPU) a tři přidané registry pro plovoucí desetinnou čárku, implementující standard IEEE754-1985 s plovoucí desetinnou čárkou. Měl také 4 KB integrované paměti RAM a byl k dispozici ve verzích 20 nebo 25 MHz. Podpora zarážky byla přidána v pozdějších modelech T801 a T805 , přičemž první z nich představovalo oddělené adresové a datové sběrnice pro zlepšení výkonu. T805 byl také později k dispozici jako součást 30 MHz.

Byl plánován vylepšený T810 , který by měl více RAM, více a rychlejších odkazů, další pokyny a vylepšený mikrokód, ale to bylo kolem roku 1990 zrušeno.

Inmos také produkoval celou řadu podpůrných čipů pro procesory transputerová, jako je C004 32 způsobů propojení přepínače a C011 a C012 „link adaptérů“, což umožnilo transputerová odkazy, které mají být připojeny k 8-bitovou sběrnici.

T400

Součástí původní strategie Inmos bylo vyrobit CPU tak malé a levné, že je lze kombinovat s jinou logikou v jednom zařízení. Ačkoli systém na čipu (SoC), jak se běžně nazývá, je nyní všudypřítomný, na počátku 80. let minulého století byl tento koncept téměř neslýchaný. Kolem roku 1983 byly zahájeny dva projekty, M212 a televizní hračka . M212 byl založen na standardním jádru T212 s přidáním diskového řadiče pro standardy ST 506 a ST 412 Shugart. TV-toy měl být základem pro herní konzoli a byl společným projektem společností Inmos a Sinclair Research .

Vazby v transvertorech T212 a T414/T424 měly hardwarové motory DMA, takže přenosy mohly probíhat souběžně s prováděním jiných procesů. Varianta návrhu, nazývaná T400, nesmí být zaměňována s pozdějším stejnojmenným transputerem, byla navržena tam, kde CPU zpracovával tyto přenosy. Tím se značně zmenšila velikost zařízení, protože 4článkové motory byly přibližně stejně velké jako celý CPU. T400 měl být použit jako jádro v tehdy nazývaných systémech na zařízeních na křemíku (SOS), nyní nazývaných a lépe známých jako systém na čipu (SoC). Právě tento design měl být součástí TV-hračky. Projekt byl zrušen v roce 1985.

T100

Ačkoli předchozí projekty SoC měly jen omezený úspěch (M212 byl prodáván po určitou dobu), mnoho návrhářů stále pevně věřilo v koncept a v roce 1987, nový projekt, byl zahájen T100, který kombinoval 8bitovou verzi transputeru CPU s konfigurovatelnou logikou na základě stavových strojů. Sada instrukčních transputerů je založena na 8bitových instrukcích a lze ji snadno použít s jakoukoli velikostí slova, která je násobkem 8 bitů. Cílovým trhem pro T100 měly být řadiče sběrnice, jako je Futurebus, a upgrade pro standardní linkové adaptéry (C011 atd.). Projekt byl zastaven, když byl spuštěn T840 (později se stal základem T9000).

- Transvertory řady T2, T4 a T8

TPCORE

TPCORE je implementace transputeru, včetně os-odkazů, který běží na FPGA.

T9000

Inmos vylepšil výkon transvertorů řady T8 zavedením T9000 (kódově pojmenovaný H1 během vývoje). T9000 sdílel většinu funkcí s T800, ale přesunul několik kusů designu do hardwaru a přidal několik funkcí pro superskalární podporu. Na rozdíl od dřívějších modelů měl T9000 místo RAM skutečnou vysokorychlostní mezipaměť 16 kB (pomocí náhodného nahrazení), ale také umožňoval její použití jako paměti a zahrnoval funkce podobné MMU, které toto vše zvládly (nazývané PMI ) . Kvůli vyšší rychlosti ukládal T9000 do mezipaměti 32 nejlepších umístění zásobníku místo tří jako v předchozích verzích.

T9000 používal pětistupňové potrubí pro ještě větší rychlost. Zajímavým přírůstkem byl seskupovač, který shromažďoval pokyny z mezipaměti a seskupoval je do větších balíků o velikosti až 8 bajtů, aby bylo potrubí napájeno rychleji. Skupiny se pak dokončily v jednom cyklu, jako by to byly jednotlivé větší instrukce pracující na rychlejším CPU.

Spojovací systém byl aktualizován na nový režim 100 MHz, ale na rozdíl od předchozích systémů již spoje nebyly směrem dolů kompatibilní. Tento nový paketový propojovací protokol se nazýval DS-Link a později tvořil základ standardu sériového propojení IEEE 1355 . T9000 také přidal hardware pro směrování linek nazývaný VCP (Virtual Channel Processor), který změnil propojení z bodu do bodu na skutečnou síť, což umožňuje vytvoření libovolného počtu virtuálních kanálů na spojích. To znamenalo, že programy si již nemusely být vědomy fyzického rozložení připojení. Rovněž byla vyvinuta řada podpůrných čipů DS-Link, včetně 32-way crossbar switch C104 a C101 link adapter.

Dlouhá zpoždění ve vývoji T9000 znamenala, že návrhy rychlejšího nákladu/obchodu již v době jeho vydání překonaly. Důsledně se jí nedařilo dosáhnout vlastního výkonnostního cíle - porazit T800 desetkrát. Když byl projekt nakonec zrušen, stále dosahoval pouze asi 36 MIPS na 50 MHz. Zpoždění výroby dalo vzniknout vtipu, že nejlepší hostitelskou architekturou pro T9000 byl zpětný projektor.

To bylo příliš mnoho na Inmos, který neměl finance potřebné k pokračování vývoje. Do této doby byla společnost prodána společnosti SGS-Thomson (nyní STMicroelectronics ), jejímž zaměřením byl trh s vestavěnými systémy, a nakonec se od projektu T9000 upustilo. Komplexně přepracovaný 32bitový transputer určený pro vestavěné aplikace, řada ST20 , byl však později vyroben pomocí některé technologie vyvinuté pro T9000. Jádro ST20 bylo začleněno do čipových sad pro aplikace set-top box a Global Positioning System (GPS).

ST20

Ačkoli to nebyl striktně transputer, byl ST20 silně ovlivněn T4 a T9 a tvořil základ T450, který byl pravděpodobně posledním z transputerů. Posláním ST20 bylo být znovu použitelným jádrem na tehdy vznikajícím trhu SoC. Původní název ST20 byl Reusable Micro Core (RMC). Architektura byla volně založena na původní architektuře T4 s datovou cestou řízenou mikrokódem. Jednalo se však o kompletní redesign s použitím VHDL jako návrhového jazyka as optimalizovaným (a přepsaným) kompilátorem mikrokódu. Projekt byl koncipován již v roce 1990, kdy bylo zjištěno, že T9 bude pro mnoho aplikací příliš velký. Vlastní projekční práce začaly v polovině roku 1992. Bylo provedeno několik zkušebních návrhů, od velmi jednoduchého procesoru ve stylu RISC se složitými instrukcemi implementovanými v softwaru pomocí pastí, až po poměrně složitý superskalární design podobný svým konceptem algoritmu Tomasulo . Konečný design vypadal velmi podobně jako původní jádro T4, i když bylo přidáno nějaké jednoduché seskupení instrukcí a mezipaměť pracovního prostoru, které pomohly s výkonem.

Přijetí

Přestože byl transputer ve srovnání s mnoha současnými designy jednoduchý, ale výkonný, nikdy nepřiblížil se svému cíli univerzálního použití v rolích CPU i mikrokontroléru. Na trhu s mikrokontroléry dominovaly na trhu 8bitové stroje, kde byly náklady nejvážnějším hlediskem. Zde byly dokonce i T2 pro většinu uživatelů příliš výkonné a nákladné.

V oblasti stolních počítačů a pracovních stanic byl transputer poměrně rychlý (pracoval s rychlostí přibližně 10 milionů instrukcí za sekundu (MIPS) při 20 MHz). Na začátku 80. let to byl vynikající výkon, ale v době, kdy byla T800 vybavena jednotkou s plovoucí desetinnou čárkou (FPU) vybavenou, ji ostatní konstrukce RISC překonaly. To by mohlo být do značné míry zmírněno, kdyby stroje používaly více transputerů, jak bylo plánováno, ale T800s stál při zavedení zhruba 400 $, což znamenalo špatný poměr cena/výkon. Bylo navrženo několik systémů pracovních stanic založených na transputeru; nejpozoruhodnější pravděpodobně je pracovní stanice Atari Transputer .

Transputer byl úspěšnější v oblasti masivně paralelních počítačů, kde na konci osmdesátých let několik prodejců vyrábělo systémy založené na transputeru. Patřily mezi ně společnosti Meiko Scientific (založená bývalými zaměstnanci Inmosu), Floating Point Systems , Parsytec a Parsys. Několik britských akademických institucí založena výzkumnou činnost při uplatňování transputerová bázi paralelních systémů, včetně Bristol polytechnická ‚s Bristol transputerová Center a University of Edinburgh ‘ s Edinburgh Souběžná superpočítačů Project. Systémy získávání dat a spouštění druhé úrovně experimentu ZEUS High Energy Physics pro urychlovač Hadron Elektron Ring Anlage (HERA) v DESY byly založeny na síti více než 300 synchronně taktovaných transputerů rozdělených do několika subsystémů. Ty ovládaly jak odečet vlastní elektroniky detektoru, tak běžely rekonstrukční algoritmy pro výběr fyzikálních událostí.

Možnosti paralelního zpracování transputeru začaly komerčně využívat pro zpracování obrazu největší světová tisková společnost RR Donnelley & Sons na počátku 90. let. Schopnost rychle transformovat digitální obrázky v rámci přípravy na tisk dala firmě značnou výhodu nad jejich konkurenty. Tento vývoj vedl Michael Bengtson v RR Donnelley Technology Center. Během několika let ukončila schopnost zpracování i stolních počítačů potřebu vlastních systémů vícenásobného zpracování pro firmu.

Německá společnost Jäger Messtechnik použila pro své rané produkty pro získávání a řízení dat v reálném čase ADwin převodníky .

Francouzská společnost postavila superpočítač Archipel Volvox s až 144 vysílači T800 a T400. Byl řízen Silicon Graphics Indigo2 se systémem UNIX a speciální kartou, která byla propojena se zadními letouny Volvox.

Transputery také našly využití v analyzátorech protokolů, jako je Siemens/Tektronix K1103, a ve vojenských aplikacích, kde architektura polí vyhovující aplikacím, jako je radar a sériové linky (které byly v 80. letech vysoké rychlosti), dobře sloužila k úspoře nákladů a hmotnosti v dílčích komunikace systému.

Transputer se také objevil v produktech souvisejících s virtuální realitou , jako je systém ProVision 100 vyrobený společností Division Limited z Bristolu, představující kombinaci procesorů Intel i860 , 80486 /33 a Toshiba HSP, společně s transputery T805 nebo T425, implementující renderovací engine, který k nim pak bylo možné přistupovat jako server prostřednictvím systémů PC , Sun SPARCstation nebo VAX .

Myriade , evropská miniaturizovaná satelitní platforma vyvinutá společnostmi Astrium Satellites a CNES a používaná satelity, jako je Picard , vychází z T805 s výnosem kolem 4 MIPS a je naplánováno, že zůstane ve výrobě přibližně do roku 2015.

Asynchronní operace komunikace a výpočtu umožnila vývoj asynchronních algoritmů, jako je například Baneův algoritmus „Asychronous Polynomial Zero Finding“. Pole asynchronních algoritmů a asynchronní implementace aktuálních algoritmů pravděpodobně bude hrát klíčovou roli při přechodu na exascale computing .

High Energy Transient Explorer 2 (HETE-2) sonda použit 4 x T805 transputerech a 8 x DSP56001 se získá asi 100 milionů instrukcí za sekundu (MIPS) výkonu.

Dědictví

Rostoucí interní paralelismus je jednou z hnacích sil vylepšení konvenčních návrhů CPU. Namísto explicitního paralelismu na úrovni vláken (jak se používá v transputeru) návrhy CPU využívaly implicitní paralelismus na úrovni instrukcí, kontrolovaly sekvence kódu pro závislosti na datech a vydávaly více nezávislých instrukcí pro různé prováděcí jednotky. Toto se nazývá superskalární zpracování. Superskalární procesory jsou vhodné pro optimalizaci provádění sekvenčně konstruovaných fragmentů kódu. Kombinace superskalárního zpracování a spekulativního provádění přinesla hmatatelné zvýšení výkonu u stávajících částí kódu - které byly většinou napsány v jazycích Pascal, Fortran, C a C ++. Vzhledem k těmto podstatným a pravidelným zlepšením výkonu stávajícího kódu existovala jen malá pobídka k přepisování softwaru do jazyků nebo stylů kódování, které odhalují větší paralelismus na úrovni úkolů.

Přesto lze model spolupracujících souběžných procesorů stále najít v klastrových výpočetních systémech, které v 21. století dominují designu superpočítačů . Na rozdíl od architektury transputerů procesorové jednotky v těchto systémech obvykle používají superskalární procesory s přístupem k podstatnému množství paměti a diskového úložiště, na kterých běží konvenční operační systémy a síťová rozhraní. V důsledku složitějších uzlů má softwarová architektura použitá pro koordinaci paralelismu v takových systémech obvykle mnohem větší váhu než v transputerové architektuře.

Základní motiv transputeru zůstává, ale byl více než 20 let maskován opakovaným zdvojnásobením počtu tranzistorů. Konstruktérům mikroprocesorů nakonec nevyhnutelně došla využití větších fyzických zdrojů, téměř ve stejnou dobu, kdy škálování technologií začalo narážet na své limity. Díky spotřebě energie, a tedy potřebám odvodu tepla, je další zvyšování hodinové frekvence nerealizovatelné. Tyto faktory vedly průmysl k řešení, která se v zásadě málo liší od řešení navrhovaných společností Inmos.

Nejvýkonnější superpočítače na světě, založené na návrzích z Columbia University a postavené jako IBM Blue Gene , jsou ztělesněním transputerového snu v reálném světě. Jsou to obrovské sestavy identických, relativně málo výkonných SoC.

Nedávné trendy se také pokusily vyřešit dilema tranzistorů způsoby, které by byly příliš futuristické i pro Inmos. Kromě přidávání komponent do matrice CPU a umístění více matric do jednoho systému moderní procesory stále více umisťují více jader do jedné matrice. Designéři transputerů se snažili do svého tranzistorového rozpočtu vměstnat i jedno jádro. Dnes mohou designéři pracující s 1000násobným zvýšením hustoty tranzistorů obvykle umístit mnoho. Jeden z nejnovějších komerčních vývojů vzešel z firmy XMOS , která vyvinula rodinu vestavěných vícejádrových vícevláknových procesorů, které silně rezonují s transputerem a Inmosem. Objevuje se nově vznikající třída vícejádrových/mnohojádrových procesorů využívajících přístup sítě na čipu (NoC), jako je procesor Cell , architektura Adapteva Epiphany, Tilera atd.

Transputer a Inmos pomohly založit Bristol ve Velké Británii jako centrum pro mikroelektronický design a inovace.

Viz také

- Adapteva

- David May (počítačový vědec)

- Snadnost (programovací jazyk)

- IEEE 1355

- Inmos

- iWarp

- Počítačový povrch Meiko

Reference

externí odkazy

- Transputer - nejčastější dotazy

- Domovská stránka transputeru Ram Meenakshisundaram

- WoTUG Skupina uplatňující principy transputerů (např. Komunikujících sekvenčních procesů (CSP)) v jiných prostředích.

- Emulátor transputeru - emuluje jeden transputer T414 (tj. Žádný FPU, žádné instrukce pro blitting) a dodává služby souboru a terminálu I/O, které byly obvykle poskytovány hostitelským počítačovým systémem.

- Emulátor transputeru na bázi PC- Jedná se o port PC původního emulátoru transpondéru T414 (nazývaného jserver) napsaného Julianem Highfieldem v polovině 90. let.

- Transputery mohou být zábavné.

- Virtuální stroj Transterpreter. -Přenosný modul runtime pro occam-pi a další jazyky na základě bajtového kódu transputeru.

- Překladač Kent Retargettable occam. -Kompilátor occam-pi.

- transputer.net. - Dokumenty a další informace o transputeru.

- Inmos absolventi Adresář bývalých zaměstnanců Inmosu, plus fotky a obecné informace. Spravuje Ken Heddings.

- Vítězové Ceny designérů prince Filipa v letech 1959 až 2009, web Design Council

- Interní systémy kosmických lodí HETE-2